# Embedded electronic circuits for cryptography, hardware security and true random number generation: an overview

This is the peer reviewed version of the following article: *Original:* Acosta, A.J., Addabbo, T., Tena-Sánchez, E. (2017). Embedded electronic circuits for cryptography, hardware security and true random number generation: an overview. INTERNATIONAL JOURNAL OF CIRCUIT THEORY AND APPLICATIONS, 45(2), 145-169 [10.1002/cta.2296]. *Availability:* This version is availablehttp://hdl.handle.net/11365/1041162 since 2018-03-30T01:01:00Z *Published:* DOI:10.1002/cta.2296 *Terms of use:* Open Access The terms and conditions for the reuse of this version of the manuscript are specified in the publishing policy. Works made available under a Creative Commons license can be used according to the terms and conditions of said license. For all terms of use and more information see the publisher's website.

(Article begins on next page)

# Embedded Electronic Circuits for Cryptography, Hardware Security and True Random Number Generation: an Overview

Antonio J. Acosta<sup>1,\*</sup>, Tommaso Addabbo<sup>2,\*</sup>, Erica Tena-Sánchez<sup>1</sup>,

<sup>1</sup> Instituto de Microelectrónica de Sevilla IMSE-CNM (CSIC/Universidad de Sevilla), Seville, Spain

<sup>2</sup> Department of Information Engineering and Mathematics University of Siena, Siena, Italy

#### SUMMARY

We provide an overview of selected crypto-hardware devices, with a special reference to the lightweight electronic implementation of encryption/decryption schemes, hash functions and true random number generators. In detail, we discuss about the hardware implementation of the chief algorithms used in private-key cryptography, public-key cryptography and hash functions, discussing some important security issues in electronic crypto-devices, related to side-channel attacks, fault injection attacks and the corresponding design countermeasures that can be taken. Finally, we provide an overview about the hardware implementation of true random number generators, presenting the chief electronic sources of randomness and the types of post-processing techniques used to improve the statistical characteristics of the generated random sequences.

KEY WORDS: Lightweight Crypto-Hardware, Hash Function, Public Key Cryptography, Private Key Cryptography, Side Channel Attack, Fault Injection Attack, Random Number Generator.

## 1. Introduction

Nowadays, cyber-security plays a key-role in everyday life, from business to the general publicsafety. Cryptography is used for authentication and encryption (bank cards, wireless telephone, e-commerce, pay-TV), access control (car lock systems, restricted areas), payment (prepaid telephone cards, e-cash), and may become the fundamental instrument of democracy with the advent of e-voting systems [1–3]. As described in a recent report, Gartner estimates endpoints of the Internet of Things will grow in the next years at a compound annual growth rate of 31.7 percent through 2020, reaching an installed base of 20.8 billion units. In year 2020, 6.6 billion "things" will ship, with about two-thirds of them consumer applications; whereas hardware spending on networked endpoints will reach 3 trillion USD [4, 5]. With such a background and forecast, it is expected that cryptographic hardware will pervade technologies with an

<sup>\*</sup>Correspondence to: acojim@imse-cnm.csic.es, addabbo@dii.unisi.it

increasing demand on energy efficiency, hardware reliability, system integration, portability and security.

In this complex scenario the involved computing power ranges within different orders of magnitude, from the foreseen computing capabilities of quantum computers to those of tiny devices like RFID tags, industrial controllers, sensor nodes and smart cards. In these latter devices the implementation of approved conventional cryptographic NIST standards, like the AES block cipher and the SHA-3 hash function, leads to unfeasible solutions in terms of timing performance, chip-area, power and computing resource consumption. This matter sets the point for the Lightweight Cryptography, i.e., the subfield of cryptography aiming to provide solutions tailored for resource-constrained devices.

According to Elsevier Scopus, the largest database of research peer-reviewed literature, since 2010about 40k documents are returned if searching the keyword 'cryptography' [6]. A huge subset of these papers deal with conceptual, algorithmic, software, hardware solutions that may be taken into account in lightweight cryptography. In the face of such a vast literature, in this work we provide a brief overview of selected crypto-hardware devices, with a special reference to the lightweight electronic implementation of encryption/decryption schemes, hash functions and true random number generators.

This paper is organized as in the following. In Sec. 2 we introduce some terminology and present an overview of the hardware implementation of the chief algorithms used in privatekey cryptography, public-key cryptography and hash functions. In Secs. 3 and 4 we introduce some important security concerns about electronic crypto-devices, discussing side-channel attacks, fault injection attacks and the corresponding countermeasures that can be taken in the hardware design. Finally, Secs. 5-8 are devised to provide an overview about the electronic implementation of true random number generators (TRNGs). In detail, in Secs. 5 and 6 we discuss about security flaws, statistical defects and predictability of TRNGs, presenting the chief sources of randomness used nowadays for their hardware implementation. In Secs. 7 and 8 we discuss an overview of the different post-processing techniques aimed to improve the statistical characteristics of the generated random sequences, and the evaluation methods used to assess the reliability of cryptographic TRNGs. Conclusion and References close the paper.

# 2. Cryptographic algorithms

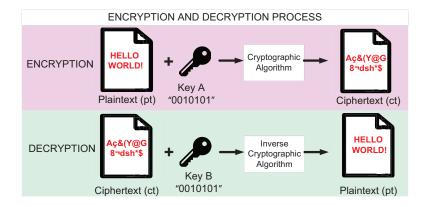

Cryptographic algorithms aim to convert secret data into a unreadable code for non authorized persons, protecting secret information from theft or alteration, and also enabling authentication. For better understanding next sections, we define the following terms. We refer to plaintexts(pt) as the input messages and ciphertexts(ct) are the output messages after encryption.Cryptographic algorithms are used in the encryption and decryption processes, where encryption transforms pt into ct using KeyA and decryption retrieves pt using KeyB, as shown in Figure 1.

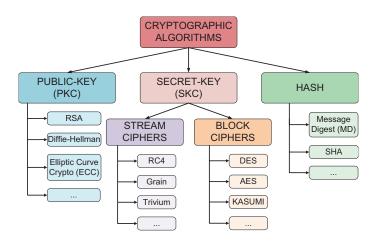

To accomplish these goals, cryptography makes use of different algorithms classified into three categories depending on the encrypt mechanism and the number of keys used in the encryption (one key, two keys or none), see Figure 2:

• Secret Key Cryptography (SKC): also called Symmetric Key Criptography, the same key is used for encryption and decryption (KeyA=KeyB). Both sender and receiver have

Figure 1. Simplified scheme of encryption and decryption processes.

to know the value of the key that, in practice, represents a shared secret between parties that is used to maintain a private information link.

- Public Key Cryptography (PKC): also called Asymmetric Key Cryptography, two different paired keys are used for encryption and decryption (KeyA ≠KeyB). KeyA is public, so any sender can use it to send private data that can only be decrypted by the owner of private key KeyB.

- Hash Functions: uses a mathematical transformation to irreversibly encrypt the information without using any key.

The selection of an specific algorithm within these familes depends on the application, security level desired, and related cost. Once selected, the next important issue is the way of implementing it physically. The algorithms can be implemented in different layers, from software down to specific hardware. The hardware implementation of cryptographic algorithms is closer to the hardware device itself, producing higher performance solutions than software, in terms of computational cost, power consumption and speed.

In embedded crypto-hardware implementations, the cryptographic algorithm is included in an FPGA or ASIC, as a part of the whole system. In many cases, to obtain the hardware implementation of a cryptographic algorithm, a digital synthesis of a hardware description language (HDL) of the algorithm is made. However, the resulting hardware implementation may not be good enough in terms of performance or security.

For this reason, the designer is often forced to select lightweight hardware-oriented cryptographic algorithms, to be used in modern portable and wearable systems in the scenario of IoT<sub>1</sub> Also, special design techniques to increase the security of the algorithms against side channel attacks must be incorporated.

# 2.1. Secret-Key/Symmetric Cryptography

SCK algorithms are classified into two groups depending on how the plaintext is encrypted: bit by bit in stream ciphers and through data blocks in block ciphers.

Figure 2. Cryptographic algorithm classification.

Stream ciphers generate a keystream that is XORed (XOR operation) with the plaintext bit by bit. They implement some kind of feedback mechanism so that the keystream is continuously changing producing different ciphertexts for the same plaintext in each encryption depending on the key, the initial value and the encryption cycle [7–9].

There are several examples of used stream ciphers. For example, in the OTP (One-Time Pad) [7] the plaintext is XORed with a truly random key bit by bit. Its main problem is that the key length has to be the same as the plaintext length, so it needs a huge amount of key bits. This cipher has been widely used but nowadays has been replaced due to its key length.

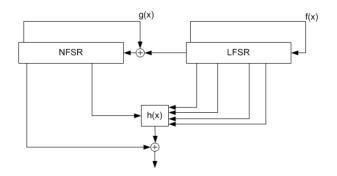

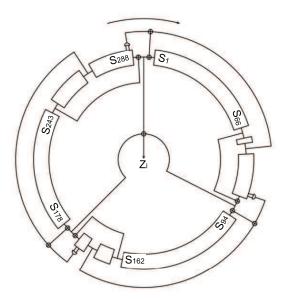

On demand of lightweight hardware implementations, the eSTREAM project [10] presented in 2004 the specific profile for hardware-oriented algorithms. Grain and Trivium ciphers were ones of the finalists. Grain [8] targets hardware environments where gate count, power consumption and memory are very limited. It is based on two shift registers and a non-linear filter function as shown in Figure 3. An FPGA implementation of Grain is presented in [11]. Trivium [9] was designed to have the most simplified structure without sacrificing security, speed or flexibility. Trivium has a 80-bit secret key and 80-bit initial value, see Figure 4. Some hardware implementations of Trivium are presented in [11,12]. Other hardware oriented stream ciphers submited to eSTREAM poyect were Mickey, Moustique and F-FCSR-H v2 among others [10].

Block ciphers encrypt one block of data at a time using the same key on each block. In general, the same plaintext block will always encrypt to the same ciphertext when using the same key in a block cipher. Some of the most commonly used block ciphers are the Data Encryption Standard (DES) [13] and Advanced Encryption Standard (AES) [14]. DES was designed in the 1970s and was adopted by the US government for commercial and unclassified government applications. DES is a block-cipher employing a 56-bit key that operates on 64-bit blocks. Some hardware implementations based on FPGA are presented in [15]. DES was abandoned due to its short key length.

In 1997, NIST initiated a public process to develop a new secure block cipher for U.S. government applications. The result, the Advanced Encryption Standard, became the official successor to DES and 3-DES in November 2001. AES encrypts data of a fixed block length (128)

Figure 3. Simplified implementation of Grain algorithm [8].

Figure 4. Simplified implementation of Trivium algorithm [9].

bits) under a key, which can either have 128, 192, or 256 bits. Currently, it is considered secure enough for critical applications. The first reported ASIC implementation of AES is in [16].

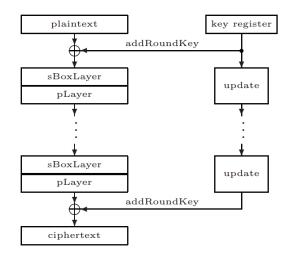

As in case of stream ciphers, due to demand of lightweight hardware implementations, new lightweight block ciphers have been presented. An example is Present [17], an ultra-lightweight block cipher notable for its compact size (about 2.5 times smaller than AES) with block size of 64 bits and the key size can be 80 bit or 128 bit, see Figure 5.

# 2.2. Public-Key/Asymmetric Cryptography

SKC needs a secure channel to exchange the key between sender and receiver, being this a serious drawback in many cases. So, in 1976 a novel branch of cryptography called Public-Key Cryptography was introduced [18]. This method allows, with use of symmetric ciphers, the key

Figure 5. Top-level description of present<sub>l</sub> [17].

exchange in a secure way even though making the communication in insecure/public channels.

PKC uses a pair of keys: the public key KeyA and the private key KeyB that belongs only to the owner. Two functions can be achieved: using a public key to authenticate that a message originated with a holder of the paired private key, or encrypting a message with a public key to ensure that only the holder of the paired private key can decrypt it [3].

PKC algorithms that are in use today for key exchange or digital signatures include RSA [19] and those based on Elliptic Curve Cryptography (ECC) among others. RSA is the most used PKC implementation, with keys from 1024 to 4096 bits typically, preventing practical attacks. A hardware implementation in FPGA of RSA is presented in [20]. PKC algorithms based upon ECCs were initially proposed independently in [21,22]. ECC is an approach to public-key cryptography based on the algebraic structure of elliptic curves over finite fields. It requires smaller keys compared to non-ECC cryptography, based on plain Galois fields, to provide equivalent security. Some FPGA and ASIC implementations can be found in [23,24].

#### 2.3. Hash Functions

Hash algorithms take input plaintexts of arbitrary length and translate them to short fixedlength output strings without using any key. These algorithms are one way encryption algorithms since once the plaintext is computed is impossible to recover neither the plaintext or the length of it.

Hash algorithms are typically used to provide a digital fingerprint of a file's contents, often used to ensure that the file has not been altered by an intruder or virus. Also they are commonly employed by many operating systems to encrypt passwords, providing a measure of the integrity of a file.

Some of the most used Hahs algorithms are:

• Message Digest (MD) algorithms [25]: A series of byte-oriented algorithms that produce a 128-bit hash value from an arbitrary-length message (MD2, MD4, MD5). An

FPGA implementation of MD5 is in [26].

• Secure Hash Algorithm (SHA) [27]: family of cryptographic hash functions published by NIST. Some hardware implementations in FPGA of SHA-256 [28] and SHA-384 and SHA-512 in [29] are presented. Some hardware implementations in FPGA of SHA-256 [28] and SHA-384 and SHA-512 are presented in [29]. Keccak [30] was selected in 2012 to become the new SHA-3 hash algorithm due to the fact that it has higher performance in hardware implementations than SHA-2 or any of the other finalists. Some lightweight hardware implementations of Keccak are presented in [31, 32].

# 3. Security on Cryptographic Devices

A cryptographic algorithm is considered to be secure in practice if there is no attack known that can break it within a reasonable amount of time and with reasonable amount of computing power. But although this algorithms are mathematically safe, their physical implementations on hardware can leak side-channel information that can be used by third parties to reveal critical data, usually the the secret key, through side-channel attacks or by fault injection attacks [33]. The main objective of cryptohardware is the design of secure cryptographic devices onto electronic platforms to implement cryptographic algorithms and store cryptographic keys in a secure way, resisting any kind of malicious attack.

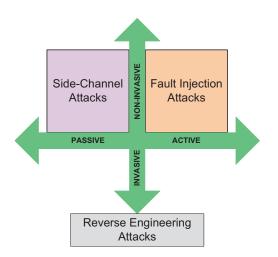

There exist different attack strategies that differ significantly in terms of cost, time, equipment, and expertise needed. They can be classified depending on two characteristics: if they are active/passive or if they are invasive/non - invasive [33]. Figure 6 summarizes the attack classification.

Invasive attacks manipulate the device, usually depackaging the chip and accessing to internal layers, while non-invasive attacks collect information provided by the device (accessible I/O, power consumption, execution time, ...) without modyfing it.

In a *passive attack*, the secret key is revealed while the cryptographic device operates in a correct way during encryption, analyzing side channel information as power consumption, timing, acoustic, or electromagnetic radiation. On the other hand, an *active attack* changes the device functionality during encryption manipulating its inputs, power supply or environment, among others. This malfunction during encryption and the outputs provided by that operation can be used to reveal the secret key.

The most powerful attacks are invasive ones, being either passive or active, but they are very expensive in terms of time, cost and effort, making in most cases an irreversible damage in the crypto-device. On the other hand, the non-invasive attacks are a big threat to cryptographic community because they usually require minimal equipment, effort and cost, and they are very effective.

We will focus on non-invasive attacks, mainly *fault injection attacks*, where the normal operation of the device is changed injecting a fault, and *side-channel attacks* (SCAs), where the secret key is retrieved by monitoring the leakaged information during normal operation of the cryptographic device.

In next subsections, SCAs and fault injection attack techniques are exposed.

Figure 6. Attack classification.

# 3.1. Side-channel Attacks

SCAs on cryptographic devices use certain physical information such as power consumption, time delay, or electromagnetic radiation to find the secret key. SCAs usually require minimal equipment, hence they are easy to carry out [33].

The most known SCAs are:

- Timing attacks [34]: the secret key can be obtained by carefully measuring the time involved in cryptographic operations, exploiting the timing variance in the operation. A practical timing attack against an actual smart card implementation of the RSA was conducted in [35]

- Power Analysis attacks [36]: it takes advantage on the dependence of power consumption in cryptocircuits on data being processed. This dependency can be exploited to retrieve secret data from electronic devices conducting Simple Power Analysis (SPA) or Differential Power Analysis (DPA) attacks. SPA takes information using a small number of power traces or even one single key, being quite challenging in practice because the attacker needs a detailed knowledge of the attacked device, so only are useful when few traces are available to the attacker. More powerful and effective are DPA attacks, being the most popular type of power analysis attack. Although it needs a huge amount of power traces, the attacker do not require detailed knowledge of the device, but power models, and can operate in a very noisy environment [33, 37–39].

- Electromagnetic Attacks (EM) [40,41]: are very similar to those based on the power consumption, but using the electromagnetic radiation of the device. Simple (SEMA) and Differential Electromagnetic Analysis (DEMA) attacks use few or a huge amount of electromagnetic traces, respectively. There are a lot of works presenting EM attacks in cryptographic hardware implementations as in [42,43].

- Acoustic attacks: the acoustic emanations of the electronic devices during encryption

have correlation with the processed data. A first work using this technique was presented in 2004 [44].

There are many SCAs in the literature for SKC, PKC and hashing. DPA attacks on block ciphers have received a lot of attention, for instance DES in [36] and AES in [45]. There is less work related to side channel vulnerability analysis on stream ciphers, but not less important. Theoretical DPA attacks on A5/1 and E0 stream ciphers are presented in [46], and on Trivium and Grain in [47].

# 3.2. Fault Injection Attacks

Fault injection attacks insert any kind of malfunction on the operation during encryption, using this wrong result to retrieve the secret key of a device.

Fault injection attacks were introduced in 1997 [48] where a fault in a computation was used to attack an RSA implementation using the Chinese Remainder Theorem (CRT). Since then, a huge amount of works have been presented in literature presenting different kind of fault injection attacks to retrieve the secret key of cryptocircuits, making a big deal to protect devices against all kind of attacks. Fault injection techniques overview can be found in [49–51]. Here is a brief summary of fault injection techniques:

- **Power supply variations**: a cheap and simple way to inject a fault is to under-power or insert a power spike in the power supply of a cryptographic device. This supply voltage variation causes malfunction on the device that can be used to reveal critical data [52].

- Variation in the external clock: they may cause malfunction in the cryptographic device. An example of this attack is presented theoretically in [53] and experimentally in [54] on Trivium stream cipher, injecting a glitch in the clock signal. There are also some fault attacks presented in block ciphers as the work in [55], where the block ciphers AES, DES, Camellia, CAST-128, SEED, and MISTY1 are attacked by injecting faults into any desired round by supplying a clock signal with a glitch.

- **Temperature variations**: raising or decreasing the temperature of the cryptographic device during encryption to produce an error [49].

- Electromagnetic pulses: an external electromagnetic field is applied near the device to cause malfunction and retrieve secret information from it [49].

# 4. Countermeasures for Cryptographic Circuits

All the above mentioned attacks are performed on physical-hardware implementation of the algorithms. There is not a unique solution to prevent side-channel and fault injection attacks, but the solutions are forced to be developed at a hardware level, being the countermeasures designed physically on silicon. In this section, a brief survey of the countermeasures against different kind of attacks is done.

# 4.1. Countermeasures Against SCAs

Since the first SCAs presented in [34, 36, 40], dozens of countermeasures have been proposed to deal with this type of intrusion. There are different kind of countermeasures against

Figure 7. Countermeasures classification [56].

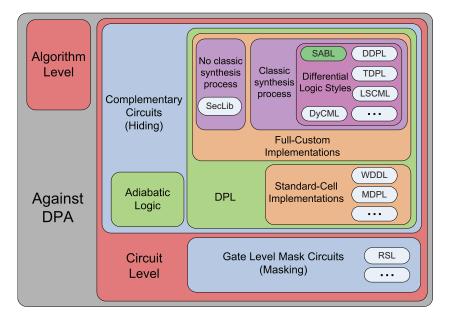

effective PA/EMA attacks to be applied depending on the abstraction level, from algorithm to layout [56–58], see Figure 7.

The use of countermeasures at algorithmic level is a hard issue due to the high dependency of the secure implementation on the specific cryptographic algorithm. This means that this technique is very specific and difficult to automate. Some approaches are presented in [59,60].

At circuit level, there are two main options that are independent of the specific algorithm used, being valid for SKC, PKC and hashing. The first one is the use of gate level mask circuits (Masking) studied in [61, 62], where the designer tries to remove the data dependency with power consumption by using a mask mixed with an intermediate value of the processed data. The other alternative at circuit level is *hiding* [63, 64], where the implementation of a logic circuit achieves theoretically the same power consumption independently of the data being processed.

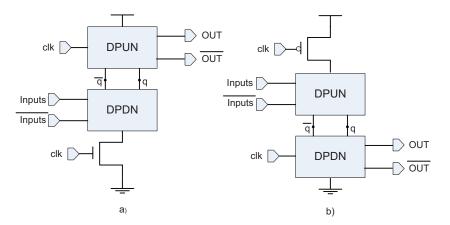

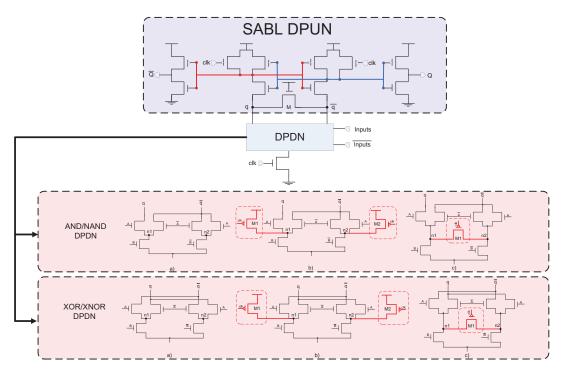

Between hiding techniques, those using Dual-rail Precharge Logic (DPL) styles with standard-cell libraries or full-custom implementations are the most effective ones. DPL gates compute always the output and its complementary, having in all clock cycles a transition in the output node, achieving thus in all clock cycles the same power consumption independent on the data being processed (Figure 8).

In DPL techniques, the ones using standard cells are WDDL [65] and MDPL [66], among others. Those using full-custom techniques, show the best results in terms of security and performance if they are correctly designed, also at layout level [56]. Some example of full-custom DPL techniques are DyCML [67], LSCML [68], SABL [63] and DDPL [69]. All these techniques use differential circuits to perform the logic operation in a pull-down circuit, alternating precharge and evaluation phases thanks to the action of pull-up circuitry. The success lies on full symmetry and lack of memory effect. Some improvements can be found in [56]. In

Figure 8. Dynamic and dual-rail gate logic style. (a) Using NMOS transistors to implement the DPDN block logic function. (b) Logic function implemented with PMOS transistors (DPUN).

Figure 9. SABL DPUN and different AND/XOR DPDN combinations: a) classic, b) double-switch solution, and c) single-switch solution.

Figure 9 it is shown the widely used SABL logic style as DPUN, with the differential DPDN network for the AND and XOR implementations, and two optimization techniques in the DPDN to remove the memory effect for the XOR gate in (b) and (c) [56].

There are some novel countermeasures presented in [70–72]. In [70] it is presented a data-

dependent delay assignment, where it is achieved a reduction in the dependency of power consumption and the processed data by introducing delays in the data paths. In [71] it is presented a so-called process obfuscation, which can be used as a countermeasure for SCAs on sensor nodes. Finally, in [72], it is presented a novel circuit concept, which decouples the main power supply from an internal power supply that is used to drive a single logic gate.

# 4.2. Countermeasures Against Fault Injection Attacks

There are two ways of protecting a cryptographic device against fault attacks [51,73]:

- Hardware countermeasures: Using prevention mechanisms, as for instance metal shields over the ASIC to prevent it from illumination and external access. There are also reported mechanisms to detect light, under-powering, clock glitch injections or optical fault injection attacks [51].

- **Design driven**: the cryptographic device is made secure against fault injection attacks, by adding redundancy in the design to check and report faults, or designing the implementation to be immune to fault injection.

Some hardware implementations of cryptographic devices to counteract fault attacks are presented in [74,75]. In [74] an AES implementation is protected from suffering from differential fault attacks, by using the error detection technique to detect the errors forced during encryption or decryption and then providing the information for taking further action, such as interrupting or redoing the AES process. In [75], it is proposed a novel Concurrent Error Detection (CED) scheme to counter fault-based attack against RSA by exploiting its multiplicative homomorphic property.

# 5. Random Number Generators

In cryptographic applications, the scope of a Random Number Generator (RNG) is to provide sequences of random integers that are deemed to be *unpredictable*. RNGs represent a fundamental class of cryptographic hardware primitives and, in most cases, the overall theoretical security of a cryptographic protocol relies on the effectiveness of the random numbers used to set-up and carry out the communication process [1-3, 76].

Nowadays, circuits and systems proposed to implement RNGs are divided in two intimately related categories, i.e., True-Random Number Generators (TRNGs) and Pseudo-Random Number Generators (PRNGs), both playing fundamental roles in cryptography. As it is made clear in the following sections, TRNGs are devised to issue random numbers exploiting the measurement of truly stochastic physical processes. On the other hand, PRNGs are deterministic finite state-machines, eventually periodic, capable to generate, within their period, binary sequences that *appear as if* they are truly random [76,77]. In few words, from a conceptual point of view, a PRNG is a device issuing and repeating indefinitely a finite random sequence, stored in its memory or generated according to different calculations. A number of efficient, interesting and advanced methods to implement PRNGs have been proposed in the literature, concerning the research areas of number theory, discrete mathematics and digital circuits [2,76–90]. Linear and nonlinear congruential generators or feedback shift registers are well known PRNGs used in a wide set of engineering fields. A basic text introducing to the

subject is the book of D. Knuth, the Art of Computer Programming [91]. A review of different PRNGs can be found in [76,77,81].

In this paper the discussion mainly focuses on TRNGs, whereas PRNGs are mentioned throughout the text only when useful.

# 5.1. A Theoretical Sketch for TRNGs

To make clear the fundamental properties of TRNGs, it is convenient to introduce some formal definitions taken from Information Theory [92]. From a theoretical point of view a TRNG is an *information source* typically modeled as an ergodic stochastic process  $\mathbf{S} = \{s_n\}, n \in \mathbb{N}$ , whose realizations are infinite sequences of symbols, chosen among the elements of a finite set (alphabet)  $\mathcal{M} = \{0, 1, \dots, m-1\} \subset \mathbb{N}$ . In most cases, the alphabet is made of numbers represented by groups of bits (e.g., binary words), or, in the simplest case (m = 2), the binary symbols  $\{0, 1\}$ . In the latter case TRNGs are often referred to as a True Random Bit Generators (TRBGs) [76].

In the following, we write  $P(s_n = a)$  to denote the probability for the TRNG to issue the symbol  $a \in \mathcal{M}$  at the time-step n. When considering joint probabilities, it is convenient to use the compact notation  $P(\bigwedge_{i=1}^k s_{n_i} = a_i)$  to denote the probability for the TRNG to issue the symbols  $a_1, \ldots, a_k$  at the time steps  $n_1, \ldots, n_k$ . Finally, we write P(A|B) to denote the conditional probability for the event A to take place once assuming the event B occurred, i.e.,  $P(A|B) = P(A \cap B)/P(B)$ , with P(B) > 0. Referring to the introduced notation, we can provide a theoretical definition for an unpredicatble TRNG.

**Definition 1.** The stochastic process  $\mathbf{S} = \{s_n\}, n \in \mathbb{N}$ , is an ideal TRNG with alphabet  $\mathcal{M} = \{0, \dots, m-1\}$  if and only if

1.  $\forall n \in \mathbb{N} \text{ and } \forall a \in \mathcal{M}, P(s_n = a) = \frac{1}{m};$

2.  $\forall k \in \mathbb{N}, k > 1$ , for all k-tuples of distinct natural numbers  $(n_1, ..., n_k)$  and for all k-tuples  $(a_1, a_2, ..., a_k) \in \mathcal{M}^k$  of symbols in  $\mathcal{M}$ , it results

$$P\left(s_{n_k} = a_k | \bigwedge_{i=1}^{k-1} s_{n_i} = a_i\right) = P(s_{n_k} = a_k).$$

(1)

An ideal TRNG is also referred to as an unpredictable TRNG.

From the above definition it follows that an unpredictable TRNG is an ergodic stochastic process issuing a sequence of statistically independent and identically distributed (i.i.d.) discrete random variables, uniformly distributed among the first m natural numbers. As a theoretical consequence, since in (1) the n-tuple  $(n_1, \ldots, n_k)$  is given without any ordering, an unpredictable TRNG has no memory of the past generated symbols and, reversing the time axis, the source has no memory of the future symbols, as well.

### 5.2. Predictability of Non-ideal TRNGs

Given the Def. 1, it is important to stress the resulting concept that a not-ideal TRNG is predictable in some sense. The security of a cryptographic protocol (e.g., an encryption/decryption scheme) can be analyzed from different sides, but at its very root level

there always lies a random number generator. If the numbers used in the protocol, deemed to be truly random, have instead some degrees of predictability, the security of the entire scheme may be compromised, e.g., by exponentially decreasing the *average number of trials* that an attacker is expected to perform to break the encryption, using the so-called *brute-force attack*.

Accordingly, the aim of any hardware TRNG is to *approximate* an ideal TRNG at its best. Information Theory provides useful theoretical tools to express how well this approximation is achieved.

**Definition 2.** The Average Shannon Entropy (ASE) of a TRNG S is equal to

$$ASE(\mathbf{S}) = \lim_{k \to \infty} -\frac{1}{k} \sum_{\beta_k \in \mathcal{M}^k} P(\beta_k) \cdot \log_2 P(\beta_k)$$

(2)

where the summation extends to the finite set collecting all binary k-tuples  $\beta_k$  with positive generation probability.

Since in (2) logarithms with base 2 are used, the result is expressed in bits/symbol. The ASE indicates, for a given TRNG, the average amount of information issued at each time-step. From the above definition it is immediate to check that for the ideal TRBG (m = 2 in Def. 1) the ASE is equal to 1 bit/time-step. Indeed, from the i.i.d. property of the binary output, for any  $k \in \mathbb{N}, k > 0$  it results

$$-\sum_{\beta_k \in \{0,1\}^k} P(\beta_k) \cdot \log_2 P(\beta_k) = 2^k \cdot \frac{1}{2^k} \log_2 2^k = k \log_2 2 = k,$$

(3)

and the limit (2) is equal to 1 bit/time-step. In such case the ASE agrees with the maximum classical Shannon Entropy for a binary source [X]. For most hardware TRNGs, an adequate estimation of (2) can result almost unfeasible, since it involves statistical distributions of any order.

## 5.3. Statistical Defects in Non-ideal TRNGs

A non-ideal TRNG fails to satisfy at least one of the two given conditions given in Def. 1. In most cases, any hardware TRNG fails both of the conditions at the same time, exhibiting *statistical defects* in its output that can be exploited to guess the most probable expected forthcoming symbols.

Statistical defects in the output sequence of TRNGs can be classified in stationary, related to the specific TRNG nominal design, or non-stationary, that may depend on the device aging or the environment (due to, e.g., external tampering, electromagnetic couplings, temperature and electronic supply voltage variations).

From a theoretical point of view, statistical defects in TRNGs originate from its statistical bias (i.e., symbols are not evenly distributed in probability) and from its memory (i.e., the probability for a symbol to be generated in the future, depends on the past generated symbols). The statistical bias provides a direct advantage to an adversary to predict the TRNG, since some symbols are simply more probable than others (intuitively, the device is similar to an unfair dice). Similarly, TRNGs affected by memory suffer from correlation between the generated symbols. Also in this case the autocorrelation function  $r_{xx}$  of a TRNG can be

Figure 10. A generic scheme representing a cryptographic TRNG.

exploited to predict its future symbols, as it can be easily shown, without loss of generality, focusing on the special case of a TRBG (m = 2 in Def. 1). Indeed, for all  $n \in \mathbb{N}, k \in \mathbb{Z}, k \geq -n$ ,

$$r_{xx}(k) = \sum_{b_1=0}^{1} \sum_{b_2=0}^{1} b_1 \cdot b_2 \cdot P(s_n = b_1, s_{n+k} = b_2) = P(s_n = 1, s_{n+k} = 1),$$

(4)

and

$$r_{xx}(0) = P(s_n = 1).$$

(5)

Recalling that  $P(s_n = 1, s_{n+k} = 1) = P(s_{n+k} = 1 | s_n = 1)P(s_n = 1)$  it directly result

$$P(s_{n+k} = 1|s_n = 1) = \frac{r_{xx}(k)}{r_{xx}(0)},$$

(6)

i.e., the probability to have the symbol  $s_{n+k} = 1$  given the symbol  $s_n$  equal to 1 can be determined directly from the knowledge of the autocorrelation function  $r_{xx}$ , that can be easily estimated using the well-known estimator

$$\langle r_{xx}(k) \rangle = \frac{1}{N-k} \sum_{n=0}^{N-k-1} s_n \cdot s_{n+k}.$$

(7)

The above discussion can be easily extended to more complex systems to show that, in general, in a TRNG statistical biasing and memory decrease its ASE. As a countermeasure, to mitigate the deterioration of the statistical characteristics of the generated sequence, in cryptographic TRNGs the last stage is a fully digital post-processor unit as shown in Fig. 10. The postprocessing is based on two different approaches, widely investigated in Cryptography and Information Theory: compression and diffusion/confusion. This topic is discussed in Sec. XX.

# 6. Source of Randomness in TRNGs

A TRNG outputs random numbers exploiting a truly stochastic physical phenomenon. For the sake of our outline, hardware TRNGs are defined as *mixed-signal circuits* that can be classified depending on the source of randomness taken into account for their *conceptual design*, i.e., based on:

- chaotic circuits;

- high-jitter oscillators;

- circuits to measure other stochastic physical processes.

Different authors have successfully proposed TRNGs exploiting each of the above approaches, and a combination is sometime used [93–95]. In the following subsections, we provide a brief review of these techniques.

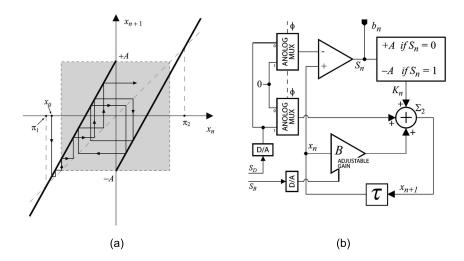

Figure 11. The Sawtooth discrete-time one-dimension piecewise linear map (a), and a TRNG exploiting this map with control signals to finely adjust the chaotic system parameters (b) [97]. In (a) the chaotic trajectory triggered by the initial condition  $x_0$  is shown using a cobweb plot [98]. The true random binary sequence is collected at the net  $b_n$  in (b).

# 6.1. Chaotic Circuits

A chaotic circuit is an analog or, more often, a mixed-signal circuit in which currents and voltages changes in time, according to a deterministic evolution rule satisfying special mathematical properties [96]. In these circuits, the time-evolution of currents and voltages is theoretically described as the state evolution of a nonlinear dynamical system exhibiting chaotic behavior.

A formal definition of chaos involves mathematical concepts introduced by Ergodic Theory, like topological transitivity, mixing and measure preserving transformations [99–101]. For the sake of our outline, adopting a qualitative point of view, chaotic dynamical systems can be described as *deterministic aperiodic systems displaying sensitive dependence on initial conditions* [98, 100]. Furthermore, let us stress that the state evolution of a n-dimension chaotic system describes a moving point in  $\mathbb{R}^n$ , defining a so-called chaotic trajectory. Well known chaotic systems are the Lorenz system, the Logistic map, the Hénon map, the Rössler system, the double rod pendulum. Other chaotic dynamical systems have been investigated in literature for their specific electronic hardware implementation, like the well known Chua's system, the Tent map or the Sawtooth map [98, 100, 102, 103].

Chaotic systems can be classified in continuous-time or discrete-time systems. In the former case the state evolution define a signal x(t),  $x : \mathbb{R} \to \mathbb{R}^n$ , being the state evolution ruled by a set of nonlinear differential equations, typically of the form  $\dot{x} = f(x)$ . In the discrete-time case the state evolution define a sequence  $\{x(t_n)\}, x : \mathbb{N} \to \mathbb{R}^n$ , being the state evolution ruled by a set of difference (recurrence) equations, typically of the form  $x_{n+1} = f(x_n)$ .

Ergodic and Information theories provide the theoretical tools to design a TRNG exploiting a chaotic dynamical system. The result, often referred as *symbolic dynamics*, is achieved by

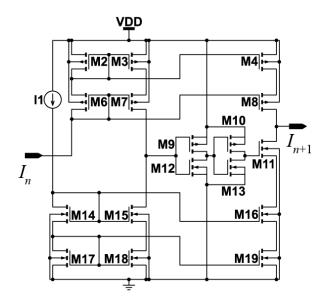

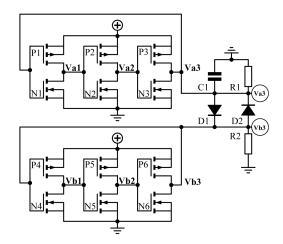

Figure 12. A CMOS implementation of the Sawtooth map in Fig. 11.a, using cascode current mirrors [104]. The circuit calculates  $I_{n+1} = f(I_n)$ , being the chaotic state variable represented by a current.

construction, defining a process devised to sample, measure and code the state of the chaotic system, adopting different strategies. The symbolic dynamics is typically obtained sampling and quantizing the projection of the system state in lower-dimensional subspaces, or coding the intersection of the chaotic trajectory with specific submanifolds, called Poincaré sections, [99–101, 103, 105]. Even if the time-evolution of the system state is ruled by deterministic equations, proper symbolic dynamics can be obtained using coding techniques, discarding some information related to the system state, defining an information source ruled by an actual stochastic process [101, 103].

In TRNG design an important class of chaotic systems is the family of discrete-time one-dimension piecewise linear maps, in which the recurrence equation  $x_{n+1} = f(x_n)$ , is given by piecewise linear functions defined on intervals, e.g.,  $f : [0,1) \rightarrow [0,1)$ . The importance of these maps comes from both the specific theoretical tools provided by Ergodic Theory for their investigation, and the specific electronic design involved for their hardware implementation [96,106–121]. For example, it has been theoretically proved that the Sawtooth map  $x_{n+1} = 2x_n \mod 1$  and the Tent map  $x_{n+1} = 1 - 2|x_n - 0.5|$  can be used to obtain the *ideal* TRNG, once the symbolic dynamics is designed to issue the sequence of binary symbols  $\{b_n\}$ , where  $b_n = '1'$  if  $x_n > 0.5$ ,  $b_n = '0'$  otherwise. Nevertheless, the statistical characteristics of the sequence generated by these systems is highly sensitive to the chaotic system parameters perturbations, causing an issue that must be carefully taken into account when designing the hardware implementation of these TRNGs [96, 97, 103, 122–125]. The electronic design of piecewise linear chaotic maps has been investigated following different approaches and targeting different applications, including true random numbers generation, secure communication and colored noise generation [96, 104, 113–121].

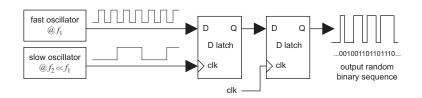

Figure 13. A schematic representation of the core structure of a TRNG exploiting high-jitter oscillators.

### 6.2. High-jitter Oscillators

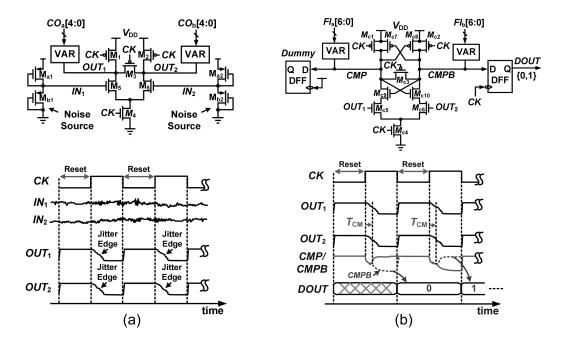

Jitter noise can be defined as the deviation of an oscillator output from its true periodicity, causing uncertainty in the low-high/high-low transition times [126–128]. The operation of TRNGs exploiting high-jitter oscillators is typically based on the interaction of independent free-running oscillators, expressively designed to exhibit high-jitter noise and having a relatively large difference between the nominal frequencies [129–133]. As shown in Fig. 13, in the simplest solution the slow oscillator is used to trigger the sampling of the fast oscillator. The frequency of the fast oscillator is typically greater than up to two order of magnitude of the slower one, being the oscillators obtained using ring-oscillators or similar structures. A further latch can be used to synchronize the digital stream to a master clock signal.

Differently from other kind of TRNGs, some solutions of this type can be implemented in fully digital processes, even in FPGAs or using micro-controllers, and this can be an advantage in several applications [134–136]. On the other hand, as discussed in the following, these TRNGs may exhibit correlation among symbols and instability of the statistical characteristics of the generated sequences, depending on the ratio between the two oscillator frequencies, on the jitter noise level, and on the sensitivity of the oscillation frequencies to aging, temperature and voltage variations [133, 136–139].

Jitter noise has been deeply investigated in literature, mainly due to its effects, e.g., in sampling devices and clock distribution in digital circuits. Most authors proposing this kind of TRNGs assume jitter noise to be completely random and Gaussian distributed, whereas in practice important deterministic components may arise due to different factors, among which the presence of deterministic variations in the supply voltage, the crosstalk between the involved oscillators, between the whole TRNG section and the neighbor circuitry or other external electromagnetic sources [128, 133, 138, 139].

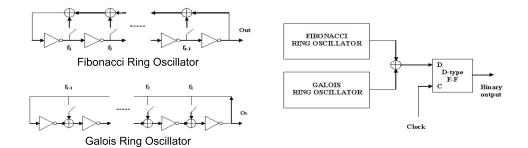

Starting from the structure shown in Fig. 13, several solutions have been proposed in literature, using voltage controlled oscillators (VCOs), chaotic systems and free running digital loops with circuit topologies inspired to hardware PRNGs, mixing the two paradigms of randomness and pseudo-randomness (Fibonacci and Galois Ring Oscillators) [94, 140]. Other authors proposed fully digital circuits capable to operate in alternating conditions between oscillations and metastability [135, 141–143].

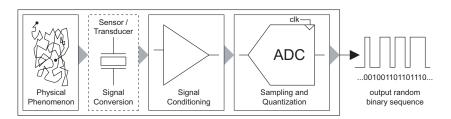

### 6.3. Circuits to Measure Other Stochastic Physical Processes

In this class of TRNGs the source of randomness is obtained from the measurement of intrinsically random physical phenomena including radioactive decay, photon detection and various sources of electronic noise in semiconductor devices (e.g., thermal, diffusion, shot, avalanche, flicker and generation/recombination noises) [95,144,144–150]. In the same class of

Figure 14. A TRNG exploiting Fibonacci and Galois Ring Oscillators [140].

Figure 15. A nonlinear network coupling two ring oscillators have been proposed in [94] to implement a chaotic 'oscillator', to substitute the conventional high-jitter oscillators in Fig. 13.

TRNGs we can also include other approaches proposed in literature, using antennas, sensors and transducers to retrieve stochastic signals from different sources like, e.g., lasers, noisy images taken with digital cameras, the Sun radiation or the atmosphere dynamics [151–153].

Depending on the exploited physical phenomenon, the implementation of these TRNGs involves the design of custom solutions expressively devised to process the stochastic signal, from the source to the output, differing case by case. A generic scheme describing this kind of systems is shown in Fig. 16.

Even if the exploited physical phenomenon offers ideal theoretical statistical properties for the task, like, e.g., the Gaussian white thermal noise in resistors, hardware implementations of TRNGs result affected by statistical bias and memory mainly due to offset, gain and nonlinearity errors in the band-limited signal conditioning stages and A/D conversion. Furthermore, in these TRNGs the stochastic signal at the source can have equivalent amplitudes as lower as few tens of microvolts, and a special care has to be taken in the design to make the device robust with respect to circuit mismatches, electromagnetic couplings with the neighbor circuitry, unforeseen aging effects, temperature and supply-voltage variations.

Figure 16. Schematic representation of the core structure of a TRNG exploiting the measurement of a stochastic physical process. When the stochastic source itself issues electric signals, as in the case of TRNGs based on electronic noise, the sensor/transducer is not necessary.

Figure 17. A TRNG exploiting electronic noise and metastability, generating one random bit DOUT each clock period (phase (a) and phase (b)) [144]. The VAR blocks are digitally-controlled networks of varactors, to finely adjust the statistical biasing of the generated random sequences.

As mentioned in Sec. 5.3, in cryptographic TRNGs the last stage issuing the random sequence is a fully digital post-processor unit based on two different ideas, widely used in Cryptography and Information Theory: compression and effective different ideas, and in the approaches is shown in Fig. 19.

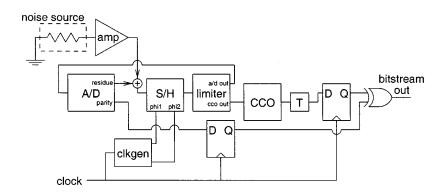

Figure 18. A TRNG exploiting a mixture of the three sources of randomness mentioned in Sec. 6: electronic noise, chaos and oscillators sampling [93]. The A/D block, with analog residuals, is actually used to implement the Sawtooth chaotic map of Fig. 11.

# 7.1. Compressors

The aim of compressors is to encode the information issued by the TRNG using fewer bits than the original representation, increasing the ASE. In literature compression algorithms have been distinguished between lossy or lossless algorithms, depending whenever the information coding is reversible (in the lossless case) or not [154]. Efficient lossless compressors require large computation resources, and in TRNGs lossy compressors are typically preferred, admitting a decrease of the throughput in return for a much less hardware complexity [155, 156].

The simplest lossy compressor proposed for a random source is the well-known Von-Neumann algorithm, capable to theoretically eliminate the statistical bias among the binary symbols 0, 1 of a TRBG. The generalization of this method, proposed in [156], requires high-complexity implementations, whereas other approaches, based on pseudo-chaotic processors or hash functions are devised to maintain a restrained hardware complexity [155, 157–159].

# 7.2. Diffusion/confusion processors

Even if an optimized compression algorithm can turn a poor TRNG in a cryptographically strong device, it is worth recalling that any given coding can not protect against a hardware failure of the TRNG, since compression can only assure the output ASE to be not lower than the input ASE. Furthermore, residual statistical defects may still be present at the output of a suboptimal compressor.

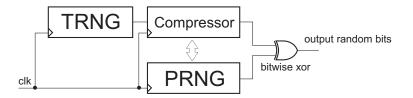

The aim of diffusion/confusion processors is to mask the residual statistical defects properly scrambling and encrypting the generated sequences. The simplest approach in cryptographic applications is to perform a bit-by-bit XOR-operation of the compressed sequence with a sequence generated by a cryptographically strong Pseudo Random Bit Generator (PRBG), as shown in Fig.19. The use of a cryptographically strong PRNG represents also a last resort against the hardware failure of the TRNG.

Figure 19. A possible scheme representing a cryptographic RNG. The kind of interaction between the true random sequence and the PRNG (dotted arrow) prior to the xoring may depend on the RNG design.

# 8. Assessment of cryptographic TRNGs

From a theoretical point of view the assessment of a cryptographic TRNG passes through the estimation of its ASE. Unfortunately, as previously mentioned, for most TRNGs an adequate estimation of (2) is unfeasible, since it involves statistical distributions of any order. Moreover, it is not possible to evaluate *a priori* the effects of possible non-stationary statistical defects. To overcome this drawback, cryptographic TRNGs are evaluated by means procedures based on standard statistical hypothesis testing [76, 160], as discussed in the following.

Statistical testing of TRNGs is an intriguing topic that would require too much text in this paper for its detailed presentation, and we limit the discussion to a conceptual sketch. In TRNG assessment the statistical hypothesis to be tested is the null hypothesis  $H_0$ : "the generator under evaluation is unpredictable". The task is accomplished focusing on one specific statistical feature of the sequences at a time (e.g., the frequency of occurrence of certain symbolic patterns) examining a finite set of finite sequences generated by the TRNG under inspection. The outcome of the test is probabilistic, i.e., it expresses the probability that the collected sequences were actually generated by a true random number generator. This probability is then compared to a given threshold to determine the acceptance/rejection of the statistical hypothesis  $H_0$ .

About the TRNG statistical testing it is worth highlighting the following remarks:

- the number of possible statistical tests is infinite, as infinite are the different statistical features to be analyzed in a random sequence. This means that any statistical test suite can not be deemed 'complete' to assess a TRNG;

- for any given setup of statistical test it is possible to build a non-random device capable to obtain the acceptance of the null hypothesis  $H_0$ .

- as a result of the above remarks, performing well in statistical testing is a necessary condition for cryptographic TRNGs, nevertheless it is non sufficient to assure their cryptographic security (i.e., their unpredictability).

Well known statistical test suites for TRNGs are the Marsaglia's DIEHARD tests and the NIST SP88.22 standard [76,160]. These tests are complex software routines to be executed by a processor, and are not suitable for being implemented in digital hardware. A low-complexity set of statistical tests designed to be implemented in digital hardware is the FIPS 140.2 test suite [161]. These latter tests are only recommended to monitor possible critical hardware failure of the TRNG, since they are too simple to assess its cryptographic reliability.

#### 9. Conclusion

We have provided an overview of selected crypto-hardware devices, with a special reference to the lightweight electronic implementation of encryption/decryption schemes, hash functions and true random number generators. In detail, we have discussed about the hardware implementation of the chief algorithms used in private-key cryptography, public-key cryptography and hash functions, discussing some important security issues in electronic crypto-devices related to side-channel attacks, fault injection attacks and the corresponding design countermeasures that can be taken. Finally, we have provided an overview about the hardware implementation of true random number generators, presenting the chief electronic sources of randomness and the types of post-processing techniques used to improve the statistical characteristics of the generated random sequences.

#### REFERENCES

- 1. S. Vaudenay, A classical introduction to cryptography. Springer, 2006.

- 2. J. Katz and K. Lindell, Introduction to modern cryptography. CRC Press, 2015.

- 3. D. R. Stinson, Cryptography: theory and practice. CRC press, 2005.

- 4. Goldman Sachs. (2014) The internet of things: Making sense of the next mega-trend. [Online]. Available: www.goldmansachs.com

- Gartner, Inc. (2015) Gartner forecast: Internet of things endpoints and associated services, worldwide, 2015. [Online]. Available: www.gartner.com

- 6. Scopus, abstract and citation database of peer-reviewed literature. bibliometric tools track, analyze and visualize research. by elsevier. [Online]. Available: www.scopus.com

- 7. G. S. Vernam, "Secret signaling system," Jul. 22 1919, uS Patent 1,310,719.

- S. M. Hell, T. Johansson, and W. Meier, "Grain: a stream cipher for constrained environments," International Journal of Wireless and Mobile Computing, vol. 2, no. 1, pp. 86–93, 2007.

- 9. C. De Cannière, "Trivium: A stream cipher construction inspired by block cipher design principles," in *International Conference on Information Security.* Springer, 2006, pp. 171–186.

- 10. ECRYPT, "The eSTREAM project," http://http:www.ecrypt.eu.org/stream/.

- J. Marmolejo-Tejada, V. Trujillo-Olaya, and J. Velasco-Medina, "Hardware implementation of grain-128, mickey-128, decim-128 and trivium," in ANDESCON, 2010 IEEE. IEEE, 2010, pp. 1–6.

- J. Mora-Gutiérrez, C. J. Jiménez-Fernández, and M. Valencia-Barrero, "Low power implementation of trivium stream cipher," in *Integrated Circuit and System Design. Power and Timing Modeling*, Optimization and Simulation. Springer, 2012, pp. 113–120.

- FIPS PUB 46, 1977 Jan 15, available from NTIS; Springfield, VA 22151 USA., "Data encryption standard."

- N. F. Pub, "197: Advanced encryption standard (aes)," Federal Information Processing Standards Publication, vol. 197, pp. 441–0311, 2001.

- 15. S. Taherkhani, E. Ever, and O. Gemikonakli, "Implementation of non-pipelined and pipelined data encryption standard (des) using xilinx virtex-6 fpga technology," in Computer and Information Technology (CIT), 2010 IEEE 10th International Conference on, June 2010, pp. 1257–1262.

- I. Verbauwhede, P. Schaumont, and H. Kuo, "Design and performance testing of a 2.29-gb/s rijndael processor," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 3, pp. 569–572, Mar 2003.

- A. Bogdanov, L. R. Knudsen, G. Leander, C. Paar, A. Poschmann, M. J. Robshaw, Y. Seurin, and C. Vikkelsoe, "Present: An ultra-lightweight block cipher," in *International Workshop on Cryptographic* Hardware and Embedded Systems. Springer, 2007, pp. 450–466.

- W. Diffie and M. Hellman, "New directions in cryptography," *IEEE Transactions on Information Theory*, vol. 22, no. 6, pp. 644–654, Nov 1976.

- R. L. Rivest, A. Shamir, and L. Adleman, "A method for obtaining digital signatures and public-key cryptosystems," *Communications of the ACM*, vol. 21, no. 2, pp. 120–126, 1978.

- G. V. Iana, P. Anghelescu, and G. Serban, "RSA encryption algorithm implemented on FPGA," 2011 International Conference on Applied Electronics, no. 1, pp. 1–4, 2011.

- N. Koblitz, "Elliptic curve cryptosystems," Mathematics of computation, vol. 48, no. 177, pp. 203–209, 1987.

- V. S. Miller, "Use of elliptic curves in cryptography," in Advances in CryptologyCRYPTO85 Proceedings. Springer, 1985, pp. 417–426.

- J. Park, J.-T. Hwang, and Y.-C. Kim, "FPGA and ASIC implementation of ECC processor for security on medical embedded system," in *Proceedings - 3rd International Conference on Information Technology* and Applications, ICITA 2005, vol. II, 2005, pp. 547–551.

- Z. Guitouni, M. Machhout, H. Mehrez, and R. Tourki, "High Performances ASIC based Elliptic Curve Cryptographic Processor over GF (2 m)," *Ijca*, no. m, pp. 1–10, 2011.

- R. L. Rivest et al., "Rfc 1321: The md5 message-digest algorithm," Internet activities board, vol. 143, 1992.

- K. Jarvinen, M. Tommiska, and J. Skytta, "Hardware implementation analysis of the md5 hash algorithm," in *Proceedings of the 38th Annual Hawaii International Conference on System Sciences*, Jan 2005, pp. 298a–298a.

- 27. P. FIPS, "180-4. secure hash standard (shs)," National Institute of Standards and Technology, 2015.

- K. K. Ting, S. C. Yuen, K.-H. Lee, and P. H. Leong, "An fpga based sha-256 processor," in *Field-Programmable Logic and Applications: Reconfigurable Computing Is Going Mainstream*. Springer, 2002, pp. 577–585.

- M. McLoone and J. V. McCanny, "Efficient single-chip implementation of sha-384 and sha-512," in Field-Programmable Technology, 2002. (FPT). Proceedings. 2002 IEEE International Conference on, Dec 2002, pp. 311–314.

- 30. G. Bertoni, J. Daemen, M. Peeters, and G. Van Assche, "Keccak," http://keccak.noekeon.org/.

- E. B. Kavun and T. Yalcin, "A lightweight implementation of keccak hash function for radio-frequency identification applications," in *International Workshop on Radio Frequency Identification: Security and Privacy Issues*. Springer, 2010, pp. 258–269.

- 32. I. San and N. At, "Compact keccak hardware architecture for data integrity and authentication on fpgas," Information Security Journal: A Global Perspective, vol. 21, no. 5, pp. 231–242, 2012.

- S. Mangard, E. Oswald, and T. Popp, Power analysis attacks: Revealing the secrets of smart cards. Springer Science & Business Media, 2008, vol. 31.

- P. C. Kocher, "Timing attacks on implementations of diffie-hellman, rsa, dss, and other systems," in Advances in CryptologyCRYPTO96. Springer, 1996, pp. 104–113.

- J.-F. Dhem, F. Koeune, P.-A. Leroux, P. Mestré, J.-J. Quisquater, and J.-L. Willems, "A practical implementation of the timing attack," in *Smart Card Research and Applications*. Springer, 1998, pp. 167–182.

- P. Kocher, J. Jaffe, and B. Jun, "Differential power analysis," in Advances in CryptologyCRYPTO99. Springer, 1999, pp. 388–397.

- 37. A. Moradi, O. Mischke, and C. Paar, "Practical evaluation of dpa countermeasures on reconfigurable hardware," in *Hardware-Oriented Security and Trust (HOST)*, 2011 IEEE International Symposium on. IEEE, 2011, pp. 154–160.

- Y. Lu, K. Boey, M. O'Neill, and J. McCanny, "Practical comparison of differential power analysis techniques on an asic implementation of the aes algorithm," in *IET Irish Signals and Systems Conference* (*ISSC'09*). IET, 2009, p. 57.

- O. Reparaz, B. Gierlichs, and I. Verbauwhede, "Generic dpa attacks: curse or blessing?" in Constructive Side-Channel Analysis and Secure Design. Springer, 2014, pp. 98–111.

- K. Gandolfi, C. Mourtel, and F. Olivier, "Electromagnetic analysis: Concrete results," in Cryptographic Hardware and Embedded SystemsCHES 2001. Springer, 2001, pp. 251–261.

- 41. Y. Hayashi, N. Homma, T. Mizuki, T. Aoki, H. Sone, L. Sauvage, and J.-L. Danger, "Analysis of electromagnetic information leakage from cryptographic devices with different physical structures," *Electromagnetic Compatibility, IEEE Transactions on*, vol. 55, no. 3, pp. 571–580, 2013.

- E. de Mulder, S. B. Ors, B. Preneel, and I. Verbauwhede, "Differential electromagnetic attack on an fpga implementation of elliptic curve cryptosystems," in 2006 World Automation Congress, July 2006, pp. 1–6.

- M. Yoshikawa, Y. Nozaki, and K. Asahi, "Electromagnetic analysis attack for a lightweight block cipher twine," in 2016 IEEE/ACES International Conference on Wireless Information Technology and Systems (ICWITS) and Applied Computational Electromagnetics (ACES), March 2016, pp. 1–2.

- 44. A. Shamir and E. Tromer, "Acoustic cryptanalysis," presentation available from http://www. wisdom. weizmann. ac. il/ tromer, 2004.

- 45. S. Mangard, N. Pramstaller, and E. Oswald, "Successfully attacking masked aes hardware implementations," in *Cryptographic Hardware and Embedded Systems-CHES 2005.* Springer, 2005, pp. 157–171.

- 46. J. Lano, N. Mentens, B. Preneel, and I. Verbauwhede, "Power analysis of synchronous stream ciphers with resynchronization mechanism," in ECRYPT Workshop, SASC-The State of the Art of Stream Ciphers, 2004, pp. 327–333.

- W. Fischer, B. M. Gammel, O. Kniffler, and J. Velten, "Differential power analysis of stream ciphers," in *Topics in Cryptology–CT-RSA 2007*. Springer, 2007, pp. 257–270.

- D. Boneh, R. DeMillo, and R. Lipton, "On the importance of checking cryptographic protocols for faults," Advances in Cryptology - EUROCRYPT', 1997.

- 49. M. Joye and M. Tunstall, Fault Analysis in Cryptography. Springer, 2012, vol. 7.

- H. Bar-El, H. Choukri, D. Naccache, M. Tunstall, and C. Whelan, "The sorcerer's apprentice guide to fault attacks," *Proceedings of the IEEE*, vol. 94, no. 2, pp. 370–382, Feb 2006.

- D. Karaklajic, J.-M. Schmidt, and I. Verbauwhede, "Hardware designer's guide to fault attacks," Very Large Scale Integration (VLSI) Systems, IEEE Transactions on, vol. 21, no. 12, pp. 2295–2306, 2013.

- O. Kömmerling and M. G. Kuhn, "Design principles for tamper-resistant smartcard processors." Smartcard, vol. 99, pp. 9–20, 1999.

- M. Hojsik and B. Rudolf, "Differential fault analysis of trivium," in *Fast Software Encryption*. Springer, 2008, pp. 158–172.

- 54. F. E. Potestad-Ordóñez, C. J. Jiménez-Fernández, and M. Valencia-Barrero, "Fault attack on fpga implementations of trivium stream cipher," *IEEE International Symposium on Circuits and Sistems*, 2016.

- 55. T. Fukunaga and J. Takahashi, "Practical fault attack on a cryptographic lsi with iso/iec 18033-3 block ciphers," in *Fault Diagnosis and Tolerance in Cryptography (FDTC), 2009 Workshop on*, Sept 2009, pp. 84–92.

- 56. E. Tena-Sanchez, J. Castro, and A. J. Acosta, "A methodology for optimized design of secure differential logic gates for dpa resistant circuits," *Emerging and Selected Topics in Circuits and Systems, IEEE Journal on*, vol. 4, no. 2, pp. 203–215, 2014.

- 57. H. Marzouqi, M. Al-Qutayri, and K. Salah, "Review of gate-level differential power analysis and fault analysis countermeasures," *Information Security*, *IET*, vol. 8, no. 1, pp. 51–66, 2014.

- T. Popp, S. Mangard, and E. Oswald, "Power analysis attacks and countermeasures," Design & Test of Computers, IEEE, vol. 24, no. 6, pp. 535–543, 2007.

- L. Goubin and J. Patarin, "Des and differential power analysis the duplication method," in Cryptographic Hardware and Embedded Systems. Springer, 1999, pp. 158–172.

- M.-L. Akkar and C. Giraud, "An implementation of des and aes, secure against some attacks," in Cryptographic Hardware and Embedded SystemsCHES 2001. Springer, 2001, pp. 309–318.

- Y. Ishai, A. Sahai, and D. Wagner, "Private circuits: Securing hardware against probing attacks," in Advances in Cryptology-CRYPTO 2003. Springer, 2003, pp. 463–481.

- O. Reparaz, B. Bilgin, S. Nikova, B. Gierlichs, and I. Verbauwhede, "Consolidating masking schemes," in Advances in Cryptology-CRYPTO 2015. Springer, 2015, pp. 764–783.

- 63. K. Tiri, M. Akmal, and I. Verbauwhede, "A dynamic and differential cmos logic with signal independent power consumption to withstand differential power analysis on smart cards," in *Solid-State Circuits Conference, ESSCIRC. Proceedings of the 28th European.* IEEE, 2002, pp. 403–406.

- 64. S. Guilley, L. Sauvage, F. Flament, V.-N. Vong, P. Hoogvorst, and R. Pacalet, "Evaluation of power constant dual-rail logics countermeasures against dpa with design time security metrics," *Computers, IEEE Transactions on*, vol. 59, no. 9, pp. 1250–1263, 2010.

- 65. K. Tiri and I. Verbauwhede, "A logic level design methodology for a secure dpa resistant asic or fpga implementation," in *Proceedings of the conference on Design, automation and test in Europe-Volume 1.* IEEE Computer Society, 2004, p. 10246.

- 66. T. Popp and S. Mangard, "Implementation aspects of the dpa-resistant logic style mdpl," in Circuits and Systems, 2006. ISCAS 2006. Proceedings. 2006 IEEE International Symposium on. IEEE, 2006, pp. 4–pp.

- 67. M. W. Allam and M. I. Elmasry, "Dynamic current mode logic (dycml): A new low-power highperformance logic style," *Solid-State Circuits, IEEE Journal of*, vol. 36, no. 3, pp. 550–558, 2001.

- I. Hassoune, F. Macé, D. Flandre, and J.-D. Legat, "Low-swing current mode logic (lscml): A new logic style for secure and robust smart cards against power analysis attacks," *Microelectronics Journal*, vol. 37, no. 9, pp. 997–1006, 2006.

- 69. M. Bucci, L. Giancane, R. Luzzi, G. Scotti, and A. Trifiletti, "Delay-based dual-rail precharge logic," Very Large Scale Integration (VLSI) Systems, IEEE Transactions on, vol. 19, no. 7, pp. 1147–1153, 2011.

- 70. I. Levi, Ö. Keren, and A. Fish, "Data-dependent delays as a barrier against power attacks," Circuits and Systems I: Regular Papers, IEEE Transactions on, vol. 62, no. 8, pp. 2069–2078, 2015.

- K. Pongaliur, Z. Abraham, A. X. Liu, L. Xiao, and L. Kempel, "Securing sensor nodes against side channel attacks," in *High Assurance Systems Engineering Symposium*, 2008. HASE 2008. 11th IEEE. IEEE, 2008, pp. 353–361.

- 72. A. Gornik, A. Moradi, J. Oehm, and C. Paar, "A hardware-based countermeasure to reduce side-channel leakage: Design, implementation, and evaluation," *Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on*, vol. 34, no. 8, pp. 1308–1319, 2015.

- 73. P. Maistri, "Countermeasures against fault attacks: The good, the bad, and the ugly," in On-Line Testing Symposium (IOLTS), 2011 IEEE 17th International. IEEE, 2011, pp. 134–137.

- 74. C.-H. Yen and B.-F. Wu, "Simple error detection methods for hardware implementation of advanced encryption standard," Computers, IEEE Transactions on, vol. 55, no. 6, pp. 720–731, 2006. 75. K. Ma, H. Liang, and K. Wu, "Homomorphic property-based concurrent error detection of rsa: a

- countermeasure to fault attack," Computers, IEEE Transactions on, vol. 61, no. 7, pp. 1040-1049, 2012.

- 76. "NIST Special Publication 800-22 Rev.1a: A statistical test suite for random and pseudorandom number generators for cryptographic applications," Apr. 2010.

- 77. J. Gentle, Random Numbers Generation and Monte Carlo Methods, 2nd ed. Springer-Verlag, 2003.

- 78. T. Addabbo, M. Alioto, S. Bernardi, A. Fort, S. Rocchi, and V. Vignoli, "Hardware-efficient PRBGs based on 1-D piecewise linear chaotic maps," in 11th IEEE International Conference on Electronics, Circuits and Systems, ICECS 2004, 2004, pp. 242–245.

- 79."The digital tent map: Performance analysis and optimized design as a source of pseudo-random bits," in Conference Record - IEEE Instrumentation and Measurement Technology Conference, vol. 2, 2004, pp. 1301–1304.

- 80. T. Addabbo, M. Alioto, A. Fort, S. Rocchi, and V. Vignoli, "Long period pseudo random bit generators derived from a discretized chaotic map," in Proceedings - IEEE International Symposium on Circuits and Systems, 2005, pp. 892-895.

- 81. P. L'Ecuyer, "Random number generation with multiple streams for sequential and parallel computing," in Proceedings - Winter Simulation Conference, vol. 2016-February, 2016, pp. 31–44.

- 82. T. Addabbo, M. Alioto, A. Fort, S. Rocchi, and V. Vignoli, "The digital tent map: Performance analysis and optimized design as a low-complexity source of pseudorandom bits," IEEE Transactions on Instrumentation and Measurement, vol. 55, no. 5, pp. 1451-1458, 2006.

- 83. -, "Low-hardware complexity prbgs based on a piecewise-linear chaotic map," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 53, no. 5, pp. 329-333, 2006.

- 84. T. Addabbo, M. Alioto, A. Fort, M. Mugnaini, S. Rocchi, and V. Vignoli, "Implementation-efficient maximum-period nonlinear congruential generators," in Conference Record - IEEE Instrumentation and Measurement Technology Conference, 2007.

- 85. T. Addabbo, M. Alioto, A. Fort, S. Rocchi, and V. Vignoli, "Maximum-period PRNGs derived from a piecewise linear one-dimensional map," in Proceedings - IEEE International Symposium on Circuits and Systems, 2007, pp. 693–696.

- 86. T. Addabbo, M. Alioto, A. Fort, A. Pasini, S. Rocchi, and V. Vignoli, "A class of maximum-period nonlinear congruential generators derived from the Rényi chaotic map," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 54, no. 4, pp. 816-828, 2007.

- 87. T. Addabbo, A. Fort, M. Mugnaini, S. Rocchi, and V. Vignoli, "On the efficient digital implementation of nonlinear congruential generators derived from the Rényi chaotic map," in Conference Record - IEEE Instrumentation and Measurement Technology Conference, 2008, pp. 1707–1711.

- 88. T. Addabbo, A. Fort, S. Rocchi, and V. Vignoli, "On the generation of pseudo-random sequences exploiting digitized chaotic systems," in European Conference on Circuit Theory and Design 2007, ECCTD 2007, 2008, pp. 639–642.

- "Digitized chaos for pseudo-random number generation in cryptography," Studies in Computational 89 Intelligence, vol. 354, pp. 67–97, 2011.

- 90. T. Addabbo, D. C. D., A. Fort, N. Petra, S. Rocchi, and V. Vignoli, "Efficient implementation of pseudochaotic piecewise linear maps with high digitization accuracies," International Journal of Circuit Theory and Applications, vol. 40, no. 1, pp. 1–14, 2012.

- 91. D. Knuth, The art of computer programming, 2nd ed. Addison-Wesley, 1981, vol. 2.

- 92. R. M. Gray, Entropy and Information Theory. Springer, 2011.

- 93. C. S. Petrie and J. A. Connelly, "A noise-based IC random number generator for applications in cryptography," IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 47, no. 5, pp. 615–621, May 2000.

- 94. I. Çiçek and G. Dündar, "A chaos based integrated jitter booster circuit for true random number generators," in Circuit Theory and Design (ECCTD), 2013 European Conference on, Sept 2013, pp. 1 - 4.

- 95. T. Yamazaki and A. Uchida, "Performance of random number generators using noise-based superluminescent diode and chaos-based semiconductor lasers," IEEE Journal of Selected Topics in Quantum Electronics, vol. 19, no. 4, pp. 0600309-0600309, July 2013.

- 96. M. Delgado-Restituto and A. Rodriguez-Vazquez, "Integrated chaos generators," Proceedings of the IEEE, vol. 90, no. 5, pp. 747–767, May 2002.

- 97. T. Addabbo, M. Alioto, A. Fort, S. Rocchi, and V. Vignoli, "A feedback strategy to improve the entropy of a chaos-based random bit generator," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 53, no. 2, pp. 326-337, 2006.

- 98. S. Hirsch, M. W.and Smale and R. Devaney, Differential equations, dynamical systems, and an introduction to chaos, 3rd ed. Academic Press, 2013.

- 99. P. Walters, An introduction to ergodic theory. Springer-Verlag, 2000.

- A. Lasota and M. C. Mackey, Chaos, Fractals and Noise Stochastic Aspects of Dynamics, 2nd ed. Springer, 1994.

- 101. A. Boyarsky and P. Góra, Laws of Chaos. Birkhäuser, 1997.

- 102. D. Chen, Z. Sun, X. Ma, and L. Chen, "Circuit implementation and model of a new multi-scroll chaotic system," *International Journal of Circuit Theory and Applications*, vol. 42, no. 4, pp. 407–424, 2014.

- T. Addabbo, A. Fort, S. Rocchi, and V. Vignoli, "Chaos based generation of true random bits," *Studies in Computational Intelligence*, vol. 184, pp. 355–377, 2009.

- 104. I. Çiçek, A. Pusane, and G. Dündar, "An integrated dual entropy core true random number generator," IEEE Transactions on Circuits and Systems II: Express Briefs, 2016, in print.

- 105. S. Ergün and S. Özoguz, "Truly random number generators based on non-autonomous continuous-time chaos," *International Journal of Circuit Theory and Applications*, vol. 38, no. 1, pp. 1–24, 2010.

- 106. T. Addabbo, A. Fort, S. Rocchi, and V. Vignoli, "Histogram test of ADCs with chaotic samples," in 2010 IEEE International Instrumentation and Measurement Technology Conference, I2MTC 2010 -Proceedings, 2010, pp. 546–549.

- 107. O. Katz, D. A. Ramon, and I. A. Wagner, "A robust random number generator based on a differential current-mode chaos," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 16, no. 12, pp. 1677–1686, Dec 2008.

- 108. T. Addabbo, A. Fort, D. Papini, S. Rocchi, and V. Vignoli, "An efficient and accurate method for the estimation of entropy and other dynamical invariants for piecewise affine chaotic maps," *International Journal of Bifurcation and Chaos*, vol. 19, no. 12, pp. 4175–4195, 2009.

- 109. ——, "Invariant measures of tunable chaotic sources: Robustness analysis and efficient estimation," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 56, no. 4, pp. 806–819, 2009.

- 110. T. Addabbo, A. Fort, M. Mugnaini, S. Rocchi, and V. Vignoli, "Statistical characterization of a chaotic piecewise linear map for uniform-distributed analog noise generation," in 16th IMEKO TC4 Int. Symp.: Exploring New Frontiers of Instrum. and Methods for Electrical and Electronic Measurements; 13th TC21 Int. Workshop on ADC Modelling and Testing Joint Session, Proc., 2008, pp. 688-693.

- 111. C.-C. Wang, J.-M. Huang, H.-C. Cheng, and R. Hu, "Switched-current 3-bit CMOS 4.0-MHz wideband random signal generator," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 6, pp. 1360–1365, June 2005.

- 112. T. Addabbo, A. Fort, S. Rocchi, and V. Vignoli, "An efficient and accurate method for computing the invariant measure of piecewise affine chaotic maps," in *Proceedings - IEEE International Symposium on Circuits and Systems*, 2008, pp. 760–763.

- 113. S. Callegari, R. Rovatti, and G. Setti, "First direct implementation of a true random source on programmable hardware," *International Journal of Circuit Theory and Applications*, vol. 33, no. 1, pp. 1–16, 2005.

- 114. T. Addabbo, M. Alioto, A. Fort, S. Rocchi, and V. Vignoli, "Uniform-distributed noise generator based on a chaotic circuit," in *Conference Record - IEEE Instrumentation and Measurement Technology Conference*, 2006, pp. 1156–1160.

- 115. M. Delgado-Restituto and A. Rodriguez-Vazquez, "Mixed-signal map-configurable integrated chaos generator for chaotic communications," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 48, no. 12, pp. 1462–1474, Dec 2001.

- A. Rodrguez-Vzquez, R. Domnguez-Castro, F. Medeiro, and M. Delgado-Restituto, "High resolution cmos current comparators: design and applications to current-mode function generation," *Analog Integrated Circuits and Signal Processing*, vol. 7, no. 2, pp. 149–165, 1995.

- 117. M. Delgado-Restituto, A. Rodriguez-Vasquez, S. Espejo, and J. L. Huertas, "A chaotic switched-capacitor circuit for 1/f noise generation," *IEEE Transactions on Circuits and Systems I: Fundamental Theory* and Applications, vol. 39, no. 4, pp. 325–328, Apr 1992.

- A. Rodriguez-Vazquez, M. Delgado, S. Espejo, and J. L. Huertas, "Switched-capacitor broadband noise generator for cmos vlsi," *Electronics Letters*, vol. 27, no. 21, pp. 1913–1915, Oct 1991.

- 119. A. Rodriguez-Vazquez, J. L. Huertas, A. Rueda, B. Perez-Verdu, and L. O. Chua, "Chaos from switchedcapacitor circuits: Discrete maps," *Proceedings of the IEEE*, vol. 75, no. 8, pp. 1090–1106, Aug 1987.

- 120. A. Rodriguez-Vazquez, A. Rueda, B. Perez-Verdu, and J. L. Huertas, "Chaos via a piecewise-linear switched-capacitor circuit," *Electronics Letters*, vol. 23, no. 12, pp. 662–663, June 1987.

- A. Rodriguez-Vazquez, J. Huertas, and L. Chua, "Chaos in switched-capacitor circuit," *IEEE Transactions on Circuits and Systems*, vol. 32, no. 10, pp. 1083–1085, Oct 1985.

T. Addabbo, A. Fort, S. Rocchi, and V. Vignoli, "Exploiting chaotic dynamics for A-D converter testing,"

- 122. T. Addabbo, A. Fort, S. Rocchi, and V. Vignoli, "Exploiting chaotic dynamics for A-D converter testing," International Journal of Bifurcation and Chaos, vol. 20, no. 4, pp. 1099–1118, 2010.

- 123. T. Addabbo, M. Alioto, A. Fort, S. Rocchi, and V. Vignoli, "A technique to design high entropy chaosbased true random bit generators," in *Proceedings - IEEE International Symposium on Circuits and*

Systems, 2006, pp. 1183–1186.

- 124. ——, "A scalable low-entropy detector to counteract the parameter variability effects in TRBGs," in 2010 IEEE International Instrumentation and Measurement Technology Conference, I2MTC 2010 Proceedings, 2010, pp. 605–609.

- 125. —, "A variability-tolerant feedback technique for throughput maximization of TRBGs with predefined entropy," Journal of Circuits, Systems and Computers, vol. 19, no. 4, pp. 879–895, 2010.

- 126. C. Sui, S. Bai, T. Zhu, C. Cheng, and D. Beetner, "New methods to characterize deterministic jitter and crosstalk-induced jitter from measurements," *IEEE Transactions on Electromagnetic Compatibility*, vol. 57, no. 4, pp. 877–884, 2015.

- 127. L. Xu, Y. Duan, and D. Chen, "A low cost jitter separation and characterization method," in *Proceedings* of the IEEE VLSI Test Symposium, vol. 2015-January, 2015.

- 128. M. Li, Jitter, Noise, and Signal Integrity at High-Speed. Pearson Education, Inc., 2008.

- 129. S. Robson, B. Leung, and G. Gong, "Truly random number generator based on a ring oscillator utilizing last passage time," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 61, no. 12, pp. 937–941, Dec 2014.