# DEPARTMENT OF INFORMATION ENGINEERING AND MATHEMATICAL SCIENCES (DIISM)

UNIVERSITY OF SIENA, ITALY

COMPUTER ARCHITECTURE GROUP

PHD PROGRAM OF INFORMATION ENGINEERING AND SCIENCE (IES)

CYCLE: XXIX

# AN EFFICIENT NOC-BASED FRAMEWORK TO IMPROVE DATAFLOW THREAD MANAGEMENT AT RUNTIME

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

| mnath Maziimbar        | Prof Antonio VICINO                 |

|------------------------|-------------------------------------|

|                        |                                     |

| $Doctoral\ Candidate:$ | Director of the PhD Program in IES: |

"Not everything that can be counted counts. Not everything that counts can be counted." – William Bruce Cameron [Informal Sociology: A Casual Introduction to Sociological Thinking]

# Acknowledgements

It was indeed an amazing journey. Similar to other PhD students, there are many times where the academic grind and struggle of completing this doctoral degree seems overwhelming. However, I must thank Prof. Antonio Vicino, Prof. Stefano Maci, Prof. Marco Maggini and Prof. Chiara Mocenni for putting me in the right place to keep me going and giving me the peace of mind to complete this doctoral work. I also have to say thank you to Alberto Scionti, Prof. Marco Pranzo and Prof. Anoop S. Kumar allowing me to explore interesting research works, and most importantly supporting me through this doctoral work. It was invaluable to have such supporters who supported my ideas and worked with me to solve them.

From the personal note, I have to thank my mother and my father for their consistent emotional support. These people are the ones more excited than me about this PhD!! I also offer sincere thanks to Mr. Prem G. Krishnan, Choti, and Bachcha for their uncountable supports in the crucial time of my PhD.

### ABSTRACT

This doctoral thesis focuses on how the application threads that are based on dataflow execution model can be managed at Network-on-Chip (NoC) level. The roots of the dataflow execution model date back to the early 1970's. Applications adhering to such program execution model follow a simple producer-consumer communication scheme for synchronising parallel thread related activities. In dataflow execution environment, a thread can run if and only if all its required inputs are available. Applications running on a large and complex computing environment can significantly benefit from the adoption of dataflow model.

In the first part of the thesis, the work is focused on the thread distribution mechanism. It has been shown that how a scalable hash-based thread distribution mechanism can be implemented at the router level with low overheads. To enhance the support further, a tool to monitor the dataflow threads' status and a simple, functional model is also incorporated into the design. Next, a software defined NoC has been proposed to manage the distribution of dataflow threads by exploiting its reconfigurability.

The second part of this work is focused more on NoC microarchitecture level. Traditional 2D-mesh topology is combined with a standard ring, to understand how such hybrid network topology can outperform the traditional topology (such as 2D-mesh). Finally, a mixed-integer linear programming based analytical model has been proposed to verify if the application threads mapped on to the free cores is optimal or not. The proposed mathematical model can be used as a yardstick to verify the solution quality of the newly developed mapping policy. It is not trivial to provide a complete low-level framework for dataflow thread execution for better resource and power management. However, this work could be considered as a primary framework to which improvements could be carried out. [303 words]

# Contents

| Li | st of | Figures                                   | ix   |

|----|-------|-------------------------------------------|------|

| Li | st of | Tables                                    | xiii |

| 1  | Inti  | roduction                                 | 1    |

|    | 1.1   | Thread management issues                  | . 3  |

|    | 1.2   | Research problem and associated solutions | 4    |

|    | 1.3   | Thesis structure                          | 7    |

| 2  | Bac   | ekground                                  | 9    |

|    | 2.1   | Dataflow threads                          | 9    |

|    | 2.2   | Hardware overview                         | 14   |

|    | 2.3   | Interconnection subsystem                 | 20   |

|    | 2.4   | Summary                                   | 28   |

| 3  | Thr   | read Distribution                         | 29   |

|    | 3.1   | Introduction                              | 29   |

|    | 3.2   | DF-Threads and its scalability            | 31   |

|    | 3.3   | Program Execution Model (PXM)             | 33   |

|    | 3.4   | Proposed Architecture                     | 35   |

|    | 3.5   | Hash Scheduling Function                  | 38   |

|    | 3.6   | Evaluation                                | 39   |

|    | 3.7   | Summary                                   | 41   |

|    | 3.8   | Acknowledgement                           | 41   |

| 4  | Moi   | nitoring                                  | 43   |

|    | 4.1   | Introduction                              | 44   |

|    | 4.2   | System model                              | 44   |

|    | 4.3   | RADA's implementation                     | 46   |

|    | 4.4   | Dealing with heterogeneity                | 48   |

|    | 4.5   | Evaluation                                | 52   |

|    | 4.6   | Summary                                   | 55   |

|    | 4.7   | Acknowledgement                           | 56   |

| 5  | Thr   | read Management at Software defined NoC   | 57   |

|    | 5.1   | Introduction                              | 58   |

|    | 5.2   | System overview                           | 59   |

|    | 53    | NoC software interface                    | 61   |

viii CONTENTS

|   | 5.4               | Proposed Network-on-Chip architecture | 62                                            |

|---|-------------------|---------------------------------------|-----------------------------------------------|

|   | 5.5               | Evaluation                            | 65                                            |

|   | 5.6               | Summary                               | 68                                            |

|   | 5.7               | Acknowledgement                       | 68                                            |

| 6 | Cus               | stomised NoC Architecture             | 69                                            |

|   | 6.1               | Introduction                          | 70                                            |

|   | 6.2               | System overview                       | 72                                            |

|   | 6.3               | Proposed Network-on-Chip architecture | 73                                            |

|   | 6.4               | Evaluation methodology                | 80                                            |

|   | 6.5               | Applicability and future improvements | 90                                            |

|   | 6.6               | Summary                               | 93                                            |

|   | 6.7               | Acknowledgement                       | 94                                            |

| 7 | Ana               | alytical Model                        | 95                                            |

|   | 7.1               | Introduction                          | 95                                            |

|   | 7.2               | Problem description and assumptions   | 97                                            |

|   | 7.3               | Mathematical formulation              | 101                                           |

|   | 7.4               | Simulation results                    | 103                                           |

|   |                   | Dimutation results                    | 100                                           |

|   | 7.5               | Summary                               | 114                                           |

|   | 7.5<br>7.6        |                                       |                                               |

| 8 | 7.6               | Summary                               | 114                                           |

| 8 | 7.6               | Summary                               | 114<br>115                                    |

| 8 | 7.6<br><b>Cor</b> | Summary                               | <ul><li>114</li><li>115</li><li>117</li></ul> |

# List of Figures

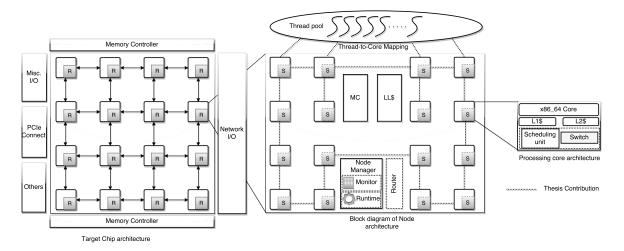

| 1.1 | Solution overview: Target chip overview for the manycores clustered pro-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | cessor. Cores are organised into clusters (i.e., nodes) connected each other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|     | through a 2D mesh. Within each node, cores and other shared resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|     | are linked via a ring. Each node has a dedicated node manager that con-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|     | trols the runtime and also monitor the system. Each core has a local                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|     | scheduling unit to distribute the threads. Blocks that are addressed in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|     | the thesis are highlighted via dotted line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8  |

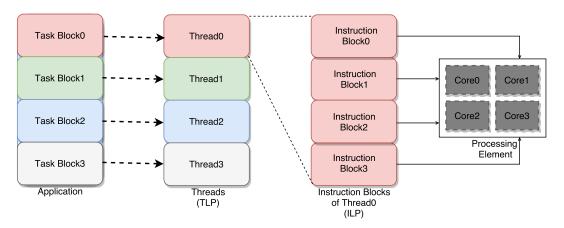

| 2.1 | Block diagram of parallelism: application level parallelism (left), thread                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|     | level parallelism (middle) and instruction level parallelism (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10 |

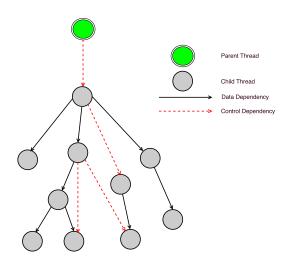

| 2.2 | Thread execution using control and data signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 |

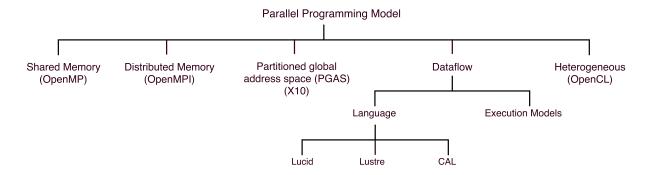

| 2.3 | Programming models classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11 |

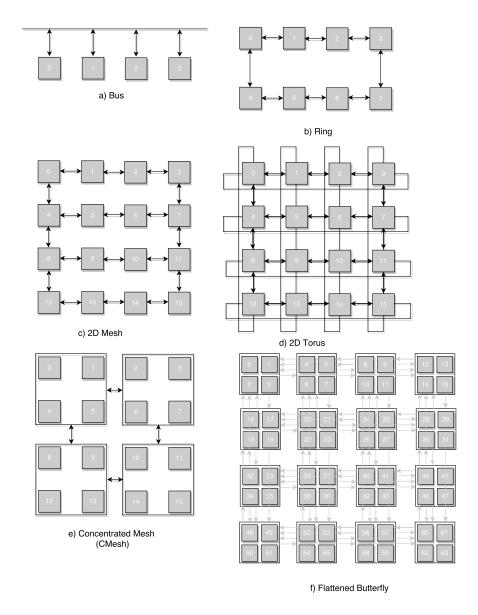

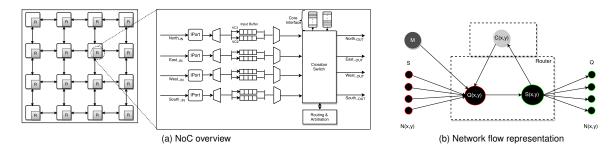

| 2.4 | Some well-known topology for interconnect subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21 |

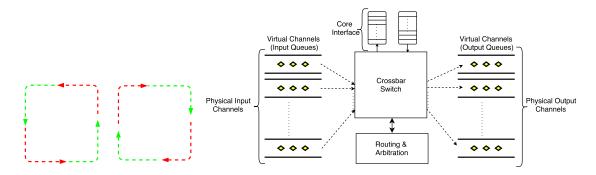

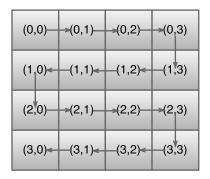

| 2.5 | XY DoR routing direction (left) and block diagram of a mesh router archi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|     | tecture is presented (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23 |

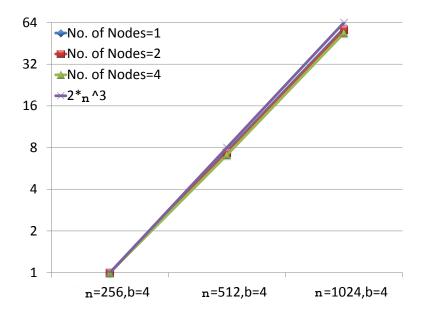

| 3.1 | Instruction count normalised to the matrix size 256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32 |

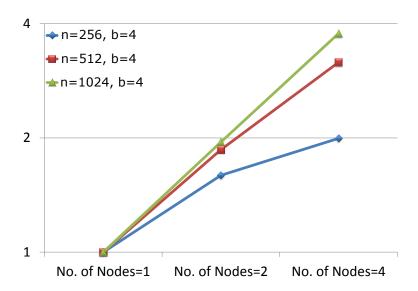

| 3.2 | Speedup of user cycles count normalised to the matrix size 256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32 |

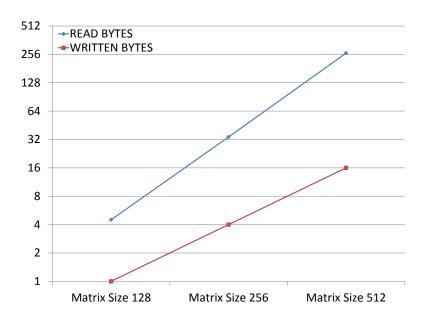

| 3.3 | Scaling of read and write operations for DF-Threads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33 |

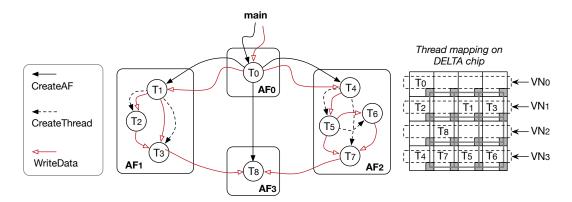

| 3.4 | A simple kernel application adhering with the proposed PXM and a possi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|     | ble mapping of threads on the PEs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35 |

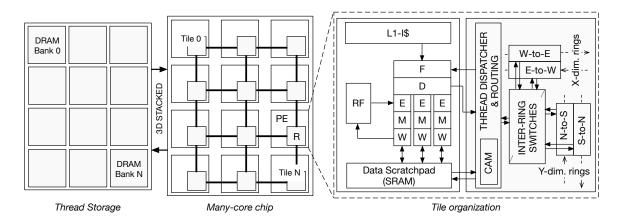

| 3.5 | Chip organization: tiles contain a PE (white box) and router (gray box).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|     | The scratchpad substitutes the traditional L1-data cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36 |

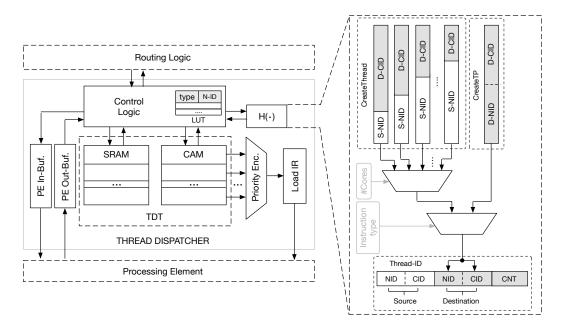

| 3.6 | Thread Dispatcher module organization (left) with the internal structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|     | of the $H(\cdot)$ function (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37 |

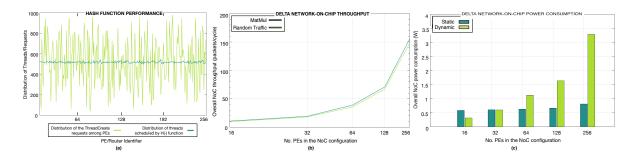

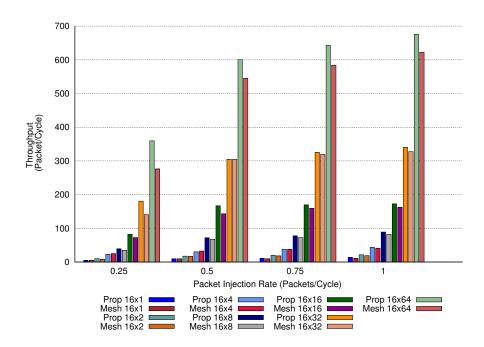

| 3.7 | NoC performance: distribution of threads on the PEs (a), average through-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|     | put (b), and power consumption (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40 |

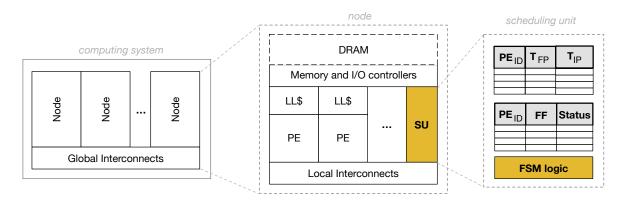

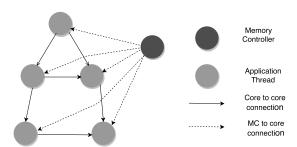

| 4.1 | System overview: the abstract machine model used to managing execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|     | of dataflow threads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45 |

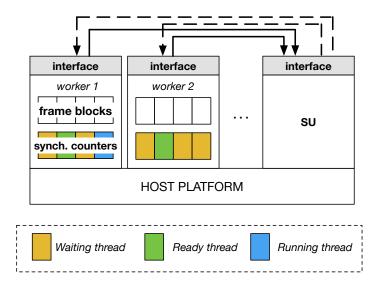

| 4.2 | Implementation of the proposed system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 47 |

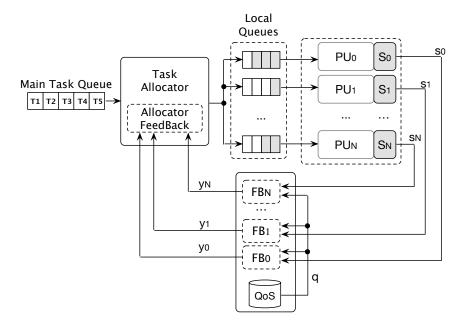

| 4.3 | Negative feedback closed-loop based task scheduling system of the RADA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48 |

| 4.4 | A code snippet of the recursive Fibonacci kernel: the code highlight the software interface exposed by RADA, which simplifies the amount of code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|     | needed to synchronise threads' activities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51 |

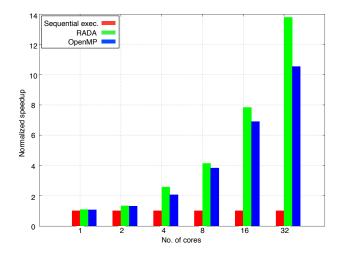

| 4.5 | Recursive Fibonacci sequence: evaluation of the RADA and OpenMP exe-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | J. |

|     | The state of the s |    |

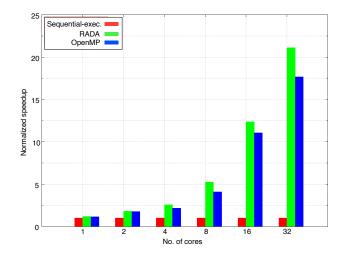

| 4.6  | Block matrix: evaluation of the RADA and OpenMP execution                      | 53 |

|------|--------------------------------------------------------------------------------|----|

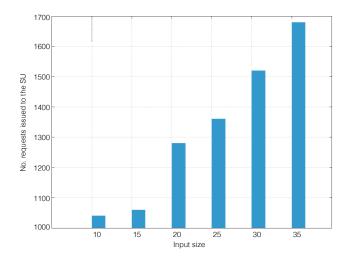

| 4.7  | Number of requests issued to the SU by the recursive Fibonacci kernel          |    |

|      | (single node, 8 cores)                                                         | 53 |

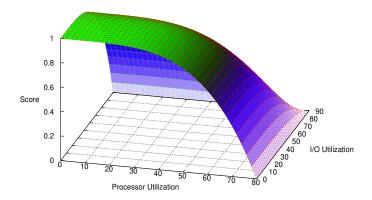

| 4.8  | Score function obtained from the execution of the BMM kernel running on        |    |

|      | host CPU and Intel Xeon Phi accelerator.                                       | 55 |

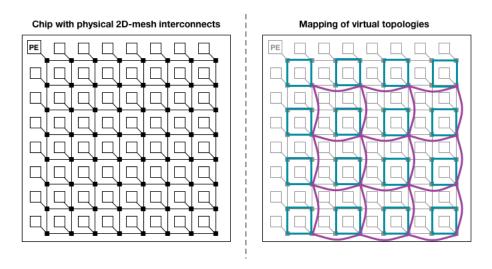

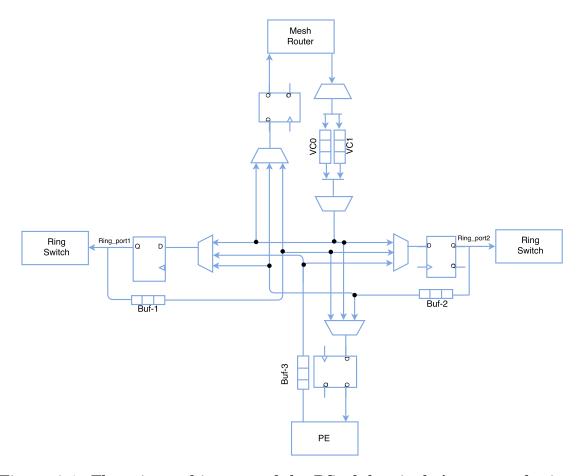

| 5.1  | Mapping between the physical network with a 2D-mesh topology, and a            |    |

|      | multi-level virtual topology. Links to the physical network are organised      |    |

|      | into local rings (blue lines) and a global 2D-mesh among rings (purple lines). | 59 |

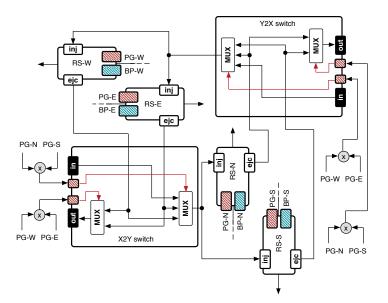

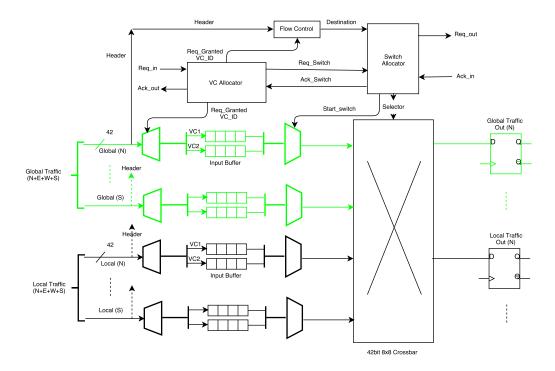

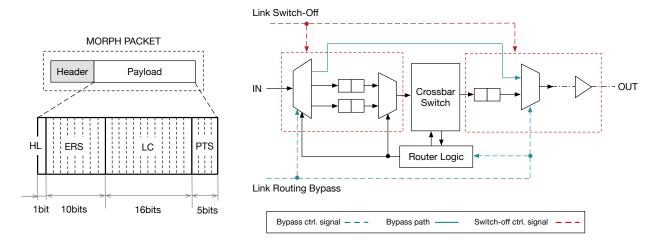

| 5.2  | The lightweight router microarchitecture. Ring stations (RSs) have injec-      |    |

|      | tion and ejection ports, and bypass (blue squares) and power-gating (red       |    |

|      | squares) bits. Inter-ring switches are power-gated depending on the state      |    |

|      | of the RS (grey circles are OR/AND gates).                                     | 63 |

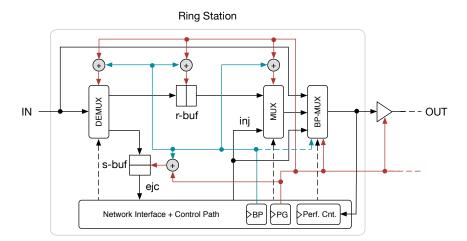

| 5.3  | The internal structure of a RS with BP/PG bits and the link counter in the     |    |

|      | network interface (dashed lines represent selection signals for multiplex-     |    |

|      | ers/demultiplexers)                                                            | 64 |

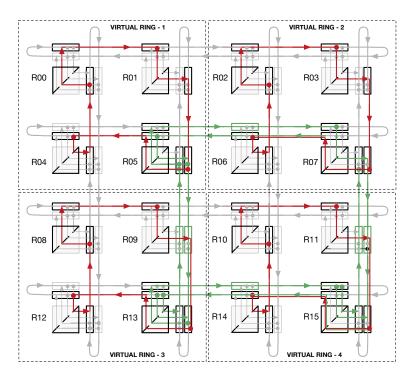

| 5.4  | An example of virtual topology mapping: Grey structures represent com-         |    |

|      | ponents (i.e., interconnections, RSs or inter-ring switches) of the router     |    |

|      | that are power-gated. Red lines correspond to active links used to build       |    |

|      | local rings, while green lines show links of the mesh. Furthermore, green      |    |

|      | boxes represented components set in bypass mode and used to construct          |    |

|      | the mesh among the virtual rings correctly.                                    | 65 |

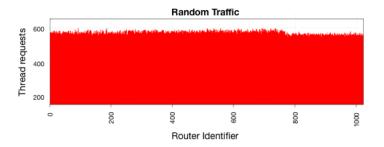

| 5.5  | Distribution of random traffic over 1024-based CMP                             | 66 |

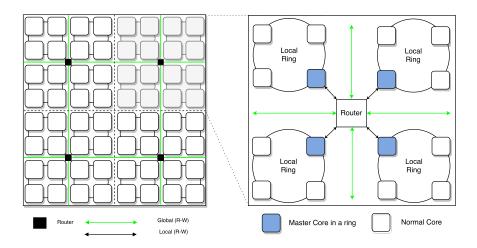

| 6.1  | An instantiation of the proposed scalable NoC: 256 PEs organised into          |    |

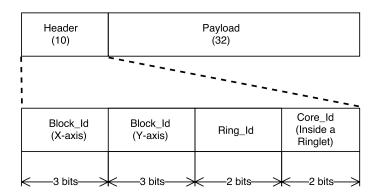

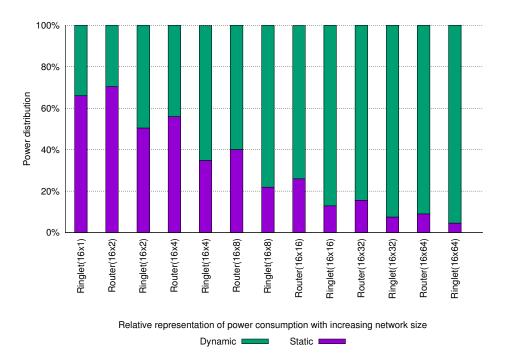

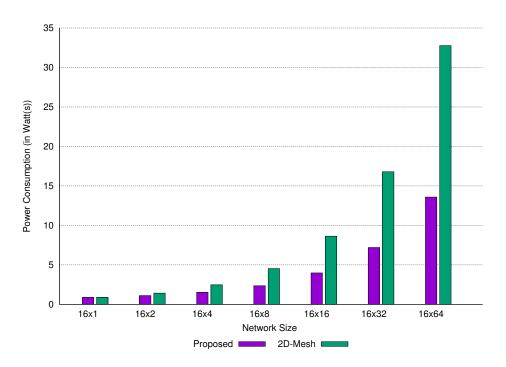

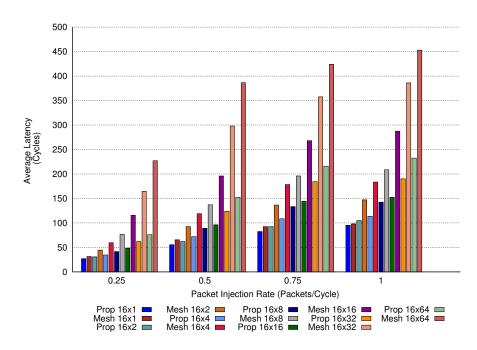

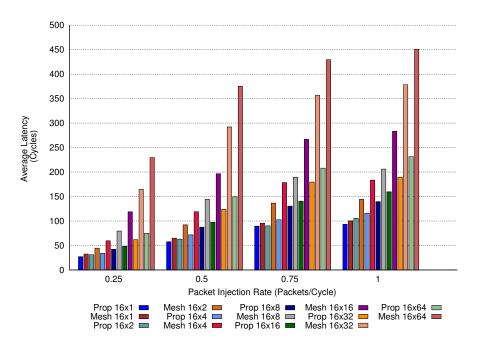

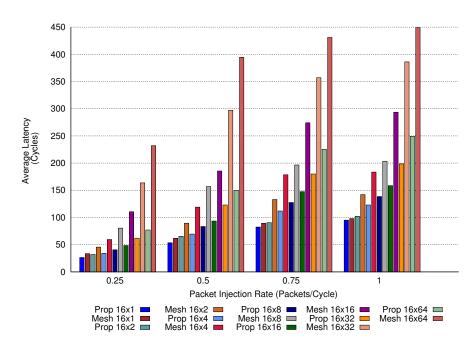

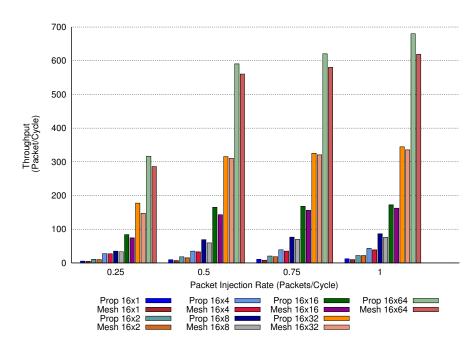

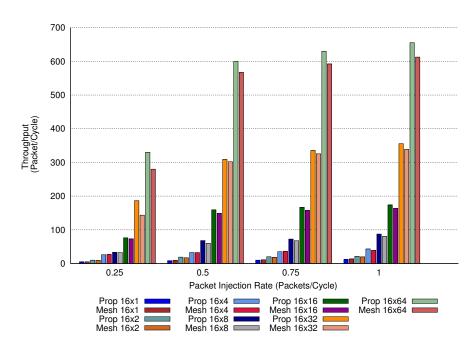

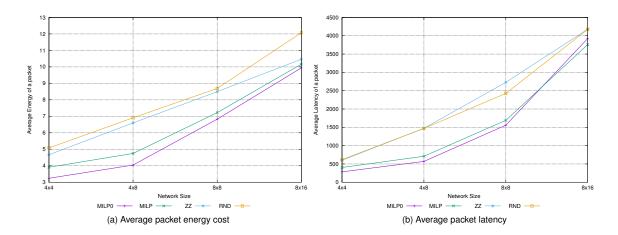

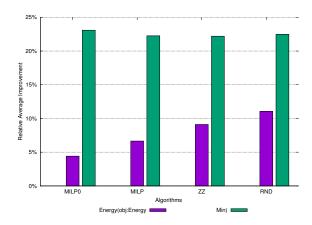

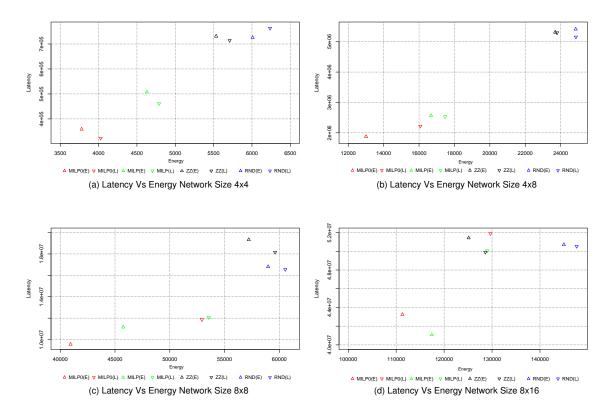

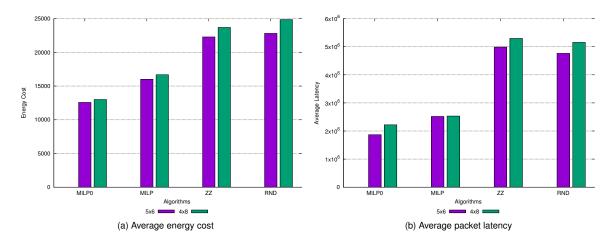

|      | $4 \times 4$ block units, each connecting four ringlets                        | 74 |